# Placement And Routing For Reconfigurable Systems

Piotr Stępień

A thesis submitted in partial fulfilment of the requirements of Bournemouth University for the degree of Doctor of Philosophy

September 2009

**Bournemouth University**

This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise its copyright rests with its author and due acknowledgement must always be made of the use of any material contained in, or derived from, this thesis.

# Abstract

Piotr Stępień

# Placement And Routing For Reconfigurable Systems

Applications using reconfigurable logic have been widely demonstrated to offer better performance over software-based solutions. However, good performance rating is often destroyed by poor reconfiguration latency - time required to reconfigure hardware to perform the new task. Recent research focus on design automation techniques to address reconfiguration latency bottleneck.

The contribution to novelty of this thesis is in new placement and routing techniques resulting in minimising reconfiguration latency of reconfigurable systems. This presents a part of design process concerned with positioning and connecting design blocks in a logic gate array. The aim of the research is to optimise the placement and interconnect strategy such that dynamic changes in system functionality can be achieved with minimum delay.

A review of previous work in the field is given and the relevant theoretical framework developed. The dynamic reconfiguration problem is analysed for various reconfigurable technologies. Several algorithms are developed and evaluated using a representative set of problem domains to assess their effectiveness.

Results obtained with novel placement and routing techniques demonstrate configuration data size reduction leading to significant reconfiguration latency improvements.

# Contents

| Li            | st of | Figures                                                   | 7  |

|---------------|-------|-----------------------------------------------------------|----|

| $\mathbf{Li}$ | st of | Tables                                                    | 9  |

| $\mathbf{Li}$ | st of | Abbreviations                                             | 10 |

| A             | cknov | wledgements                                               | 13 |

| D             | eclar | ation                                                     | 14 |

| 1             | Intr  | oduction                                                  | 15 |

|               | 1.1   | The Demand for Reconfigurable Systems                     | 16 |

|               | 1.2   | Limitations of Reconfigurable Hardware                    | 20 |

|               | 1.3   | Design Support For Reconfigurable Systems                 | 20 |

|               | 1.4   | Scope and Objectives                                      | 21 |

|               | 1.5   | Thesis outline                                            | 21 |

| <b>2</b>      | Lite  | erature review                                            | 23 |

|               | 2.1   | Reconfigurable System Definition                          | 23 |

|               | 2.2   | Reconfigurable Systems Implementation                     | 24 |

|               | 2.3   | FPGA Architecture                                         | 25 |

|               |       | 2.3.1 FPGA Programming Technologies                       | 26 |

|               |       | 2.3.2 FPGA Logic Block Architecture                       | 26 |

|               |       | 2.3.3 FPGA Routing Architecture                           | 27 |

|               | 2.4   | Design Automation                                         | 29 |

|               |       | 2.4.1 Design Techniques for One Time Programmable Systems | 29 |

|               | 2.5   | Configuration Interface Architecture                      | 31 |

|               |       | 2.5.1 Serial Configuration Data Distribution              | 31 |

|               |       | 2.5.2 Parallel Configuration Data Distribution            | 32 |

|               | 2.6   | Support for Reconfiguration                               | 33 |

|   |              | 2.6.1            | Partial Reconfiguration                        | 33       |

|---|--------------|------------------|------------------------------------------------|----------|

|   |              | 2.6.2            | Reconfiguration Latency                        | 34       |

|   | 2.7          | Dynan            | - ·                                            | 36       |

|   | 2.8          |                  |                                                | 36       |

|   |              | 2.8.1            |                                                | 37       |

|   |              | 2.8.2            |                                                | 38       |

|   |              | 2.8.3            | Temporal Partitioning at the Behavioural Level | 38       |

|   |              | 2.8.4            |                                                | 39       |

|   | 2.9          | Recon            | figurable System Framework                     | 40       |

|   | 2.10         |                  |                                                | 41       |

|   |              |                  |                                                | 41       |

|   |              | 2.10.2           | Placement Algorithms Overview                  | 42       |

|   | 2.11         |                  |                                                | 44       |

|   |              |                  | ·                                              | 46       |

|   |              |                  |                                                | 47       |

|   |              |                  |                                                | 47       |

|   | 2.12         |                  | v 0                                            | 48       |

|   |              |                  |                                                | 50       |

| 3 | Dec          |                  | al and Dessenab Mathedalam                     | 52       |

| 3 | 3.1          | 0                |                                                | 52       |

|   | $3.1 \\ 3.2$ | -                | 1                                              | 52<br>55 |

|   | 3.2<br>3.3   | 0                |                                                | 55<br>55 |

|   | ე.ე          | 3.3.1            |                                                | 55<br>56 |

|   | 3.4          |                  | I                                              | 50<br>64 |

|   | 0.4          | 3.4.1            |                                                | 64<br>64 |

|   |              | 3.4.1<br>3.4.2   |                                                | 04<br>66 |

|   | 3.5          |                  |                                                | 67       |

|   | 5.5          | 3.5.1            | 0                                              | 69       |

|   |              |                  | · 0                                            | 69<br>69 |

|   |              | $3.5.2 \\ 3.5.3$ | 0                                              |          |

|   |              |                  |                                                | 72<br>76 |

|   |              | 3.5.4            |                                                | 76<br>70 |

|   | <u>а</u> с   | 3.5.5<br>D ·     |                                                | 79<br>21 |

|   | 3.6          | -                | v v                                            | 81       |

|   |              | 3.6.1            | 0 11                                           | 81       |

|   |              | 3.6.2            |                                                | 81       |

|   | o –          | 3.6.3            |                                                | 82       |

|   | 3.7          |                  | 0                                              | 84       |

|   |              | 3.7.1            |                                                | 84       |

|   |              | 3.7.2            | Ĩ                                              | 85       |

|   | 3.8          | Multi-           | context Routing Algorithm Evaluation           | 86       |

|          |                                                                                                       | 3.8.1 Multi-context Routing Algorithm Criteria 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                                                                       | 3.8.2 Multi-context Routing Cost Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |                                                                                                       | 3.8.3 Framework Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          | 3.9                                                                                                   | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          | <b>D</b> •4                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4        |                                                                                                       | ream Size Reduction Implementation 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          | 4.1                                                                                                   | Benchmark Bitstreams Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          | 4.9                                                                                                   | 4.1.1 Bitstream Size Reduction Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          | 4.2                                                                                                   | Placement Algorithm Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |                                                                                                       | 4.2.1 Placement Algorithm Criteria                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |                                                                                                       | 4.2.2 Dynamic Location Cost Schedule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |                                                                                                       | 4.2.3 Placement Cost Function $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                     |

|          | 4.9                                                                                                   | $4.2.4  \text{Next Step Criteria}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 4.3                                                                                                   | Routing Algorithm Evaluation $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |                                                                                                       | 4.3.1 Routing Algorithm Criteria $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                  |

|          | 4 4                                                                                                   | 4.3.2 Routing Cost Function $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                       |

|          | 4.4                                                                                                   | $\Gamma \text{iming Analysis} \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | 4.5                                                                                                   | $Experimental Results \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                              |

|          | 4.6                                                                                                   | $Pins allocation \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 4.7                                                                                                   | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>5</b> | Mul                                                                                                   | i–Context Placement and Routing Implementation 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5        | <b>Mul</b><br>5.1                                                                                     | i–Context Placement and Routing Implementation 111<br>Designs Similarity Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5        |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5        | 5.1                                                                                                   | Designs Similarity Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5        | 5.1                                                                                                   | Designs Similarity Analysis       111         Placement Algorithm Evaluation       112                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5        | 5.1                                                                                                   | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1Placement Algorithm Criteria112                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5        | 5.1                                                                                                   | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1Placement Algorithm Criteria1125.2.2Dynamic Location Cost Schedule113                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5        | 5.1                                                                                                   | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1Placement Algorithm Criteria1125.2.2Dynamic Location Cost Schedule1135.2.3Placement Cost Function113                                                                                                                                                                                                                                                                                                                                                                              |

| 5        | 5.1<br>5.2                                                                                            | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1Placement Algorithm Criteria1125.2.2Dynamic Location Cost Schedule1135.2.3Placement Cost Function1135.2.4Next Step Criteria113                                                                                                                                                                                                                                                                                                                                                    |

| 5        | 5.1<br>5.2                                                                                            | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1Placement Algorithm Criteria1125.2.2Dynamic Location Cost Schedule1135.2.3Placement Cost Function1135.2.4Next Step Criteria113Routing Algorithm Evaluation114                                                                                                                                                                                                                                                                                                                     |

| 5        | 5.1<br>5.2                                                                                            | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1Placement Algorithm Criteria1125.2.2Dynamic Location Cost Schedule1135.2.3Placement Cost Function1135.2.4Next Step Criteria113Routing Algorithm Evaluation1145.3.1Routing Algorithm Criteria114                                                                                                                                                                                                                                                                                   |

| 5        | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                                                         | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1 Placement Algorithm Criteria1125.2.2 Dynamic Location Cost Schedule1135.2.3 Placement Cost Function1135.2.4 Next Step Criteria113Routing Algorithm Evaluation1145.3.1 Routing Algorithm Criteria1145.3.2 Routing Cost Function114                                                                                                                                                                                                                                                |

| 5        | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                                                         | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1Placement Algorithm Criteria1125.2.2Dynamic Location Cost Schedule1135.2.3Placement Cost Function1135.2.4Next Step Criteria113Routing Algorithm Evaluation1145.3.1Routing Algorithm Criteria1145.3.2Routing Cost Function114Experimental Results114                                                                                                                                                                                                                               |

| 5        | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul>                                             | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1 Placement Algorithm Criteria1125.2.2 Dynamic Location Cost Schedule1135.2.3 Placement Cost Function1135.2.4 Next Step Criteria113Routing Algorithm Evaluation1145.3.1 Routing Algorithm Criteria1145.3.2 Routing Cost Function1145.4.1 Simultaneous Placement and Routing Results114                                                                                                                                                                                             |

| 5        | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul>                           | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1 Placement Algorithm Criteria1125.2.2 Dynamic Location Cost Schedule1135.2.3 Placement Cost Function1135.2.4 Next Step Criteria113Routing Algorithm Evaluation1145.3.1 Routing Algorithm Criteria1145.3.2 Routing Cost Function1145.4.1 Simultaneous Placement and Routing Results1145.4.1 Simultaneous Placement and Routing Results115                                                                                                                                          |

| 5        | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul>                           | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1 Placement Algorithm Criteria1125.2.2 Dynamic Location Cost Schedule1135.2.3 Placement Cost Function1135.2.4 Next Step Criteria113Routing Algorithm Evaluation1145.3.1 Routing Algorithm Criteria1145.3.2 Routing Cost Function1145.4.1 Simultaneous Placement and Routing Results1145.4.1 Simultaneous Placement and Routing Results115Frames Sharing Analysis115Fining Analysis117                                                                                              |

| 5        | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1 Placement Algorithm Criteria1125.2.2 Dynamic Location Cost Schedule1135.2.3 Placement Cost Function1135.2.4 Next Step Criteria1136.3.1 Routing Algorithm Evaluation1145.3.2 Routing Cost Function1145.4.1 Simultaneous Placement and Routing Results1145.4.1 Simultaneous Placement and Routing Results1145.4.1 CLB Blocks Sharing117                                                                                                                                            |

| 5        | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> </ul> | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1 Placement Algorithm Criteria1125.2.2 Dynamic Location Cost Schedule1135.2.3 Placement Cost Function1135.2.4 Next Step Criteria113Routing Algorithm Evaluation1145.3.1 Routing Algorithm Criteria1145.3.2 Routing Cost Function1145.4.1 Simultaneous Placement and Routing Results114Frames Sharing Analysis1175.6.1 CLB Blocks Sharing117Pins Allocation118                                                                                                                      |

| 5        | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                                           | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1 Placement Algorithm Criteria1125.2.2 Dynamic Location Cost Schedule1135.2.3 Placement Cost Function1135.2.4 Next Step Criteria1135.2.4 Next Step Criteria1145.3.1 Routing Algorithm Evaluation1145.3.2 Routing Cost Function1145.3.1 Routing Algorithm Criteria1145.4.1 Simultaneous Placement and Routing Results1145.4.1 Simultaneous Placement and Routing Results1175.6.1 CLB Blocks Sharing117Pins Allocation118Scalability Of The Approach118Frames Overlapping Problem118 |

| 5        | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                                           | Designs Similarity Analysis111Placement Algorithm Evaluation1125.2.1 Placement Algorithm Criteria1125.2.2 Dynamic Location Cost Schedule1135.2.3 Placement Cost Function1135.2.4 Next Step Criteria1136.3.1 Routing Algorithm Evaluation1145.3.2 Routing Cost Function1145.3.1 Simultaneous Placement and Routing Results1145.4.1 Simultaneous Placement and Routing Results1175.6.1 CLB Blocks Sharing117Pins Allocation118Scalability Of The Approach118                                                                                            |

|              |                | 5.10.2 Single Block Configuration          | . 120 |  |

|--------------|----------------|--------------------------------------------|-------|--|

|              | 5.11           | Summary                                    | . 123 |  |

| 6            | Con            | clusions and Future Work                   | 126   |  |

|              | 6.1            | Summary of the Contribution                | . 126 |  |

|              |                | 6.1.1 Single Context Approach              | . 126 |  |

|              |                | 6.1.2 Multi–Context Approach               | . 127 |  |

|              | 6.2            | Solution Scalability                       | . 128 |  |

|              | 6.3            | Areas of Improvement and Future Directions |       |  |

| $\mathbf{A}$ | App            | pendix                                     | 131   |  |

|              | A.1            | Bitstream Comparison Tool                  | . 131 |  |

|              | A.2            | Java Place and Route                       | . 147 |  |

| Re           | References 153 |                                            |       |  |

# List of Figures

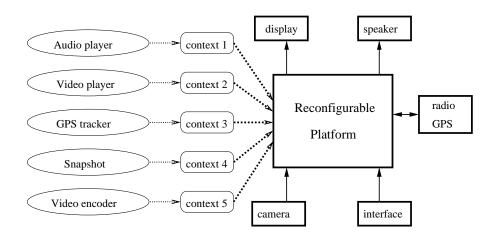

| 1  | Example of a multi–context design using a single reconfigurable platform.        | 18 |

|----|----------------------------------------------------------------------------------|----|

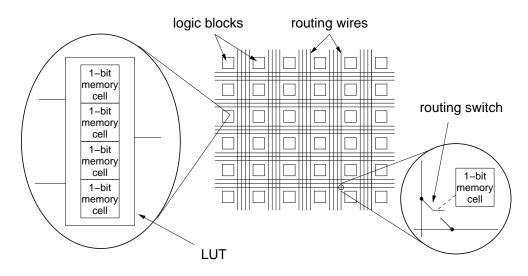

| 2  | Example of island-style configurable logic architecture based<br>on Betz (1999). | 25 |

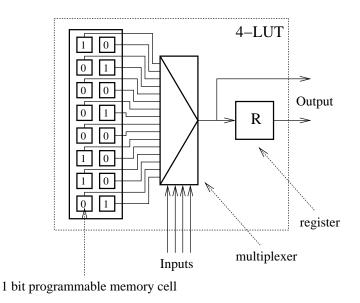

| 3  | FPGA logic block with 4–input LUT and register.                                  | 27 |

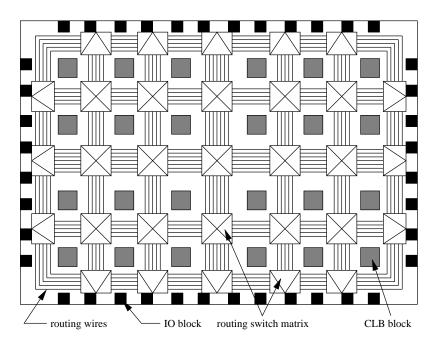

| 4  | Example of island–style routing based FPGA based on Hauck (2008).                | 28 |

| 5  | Typical Design Flow for configurable systems based on Vasilko                    |    |

| -  | (2000a).                                                                         | 30 |

| 6  | Example of Serial Configuration Data Interface.                                  | 32 |

| 7  | Example of Parallel Configuration Data Interface.                                | 33 |

| 8  | Multiple–context configuration memory from Vasilko (2000a).                      | 34 |

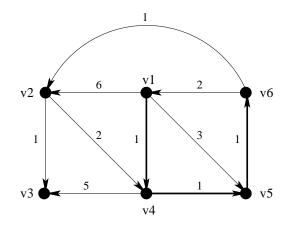

| 9  | FPGA routing example                                                             | 45 |

| 10 | Example of edge–weighted directed graph                                          | 46 |

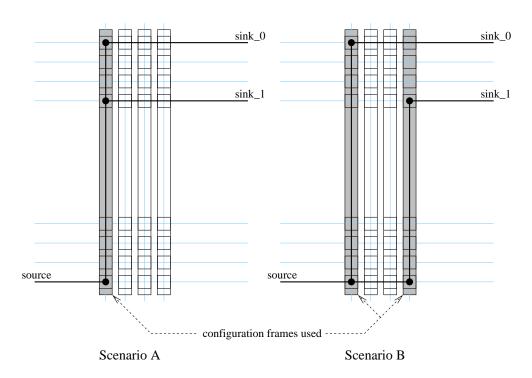

| 11 | Two design implementations with different configuration data                     |    |

|    | sizes: Scenario $A = 12$ frames, Scenario $B = 4$ frames                         | 53 |

| 12 | Example of multi-design project using the same platform                          | 54 |

| 13 | Example of Xilinx Virtex single programmable cell                                | 58 |

| 14 | Example of Xilinx Virtex configuration architecture controlling                  |    |

|    | a single programmable cell                                                       | 59 |

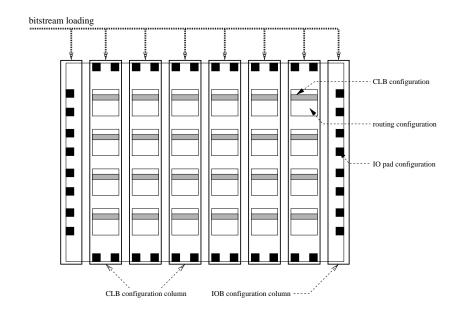

| 15 | Example of Xilinx Virtex FPGA configuration columns of frames                    |    |

|    | architecture.                                                                    | 60 |

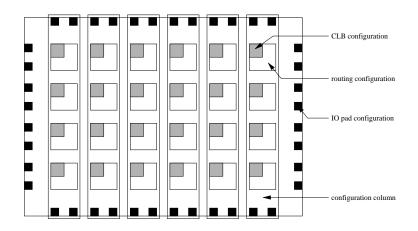

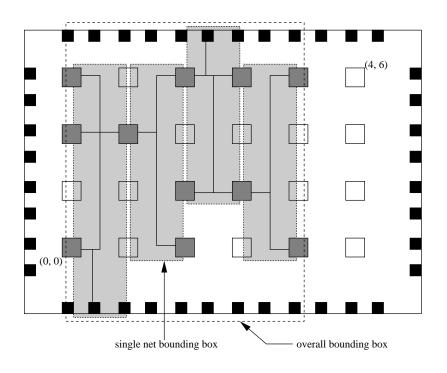

| 16 | Example of an FPGA CLB array seen from the configuration                         |    |

|    | data architecture point of view.                                                 | 62 |

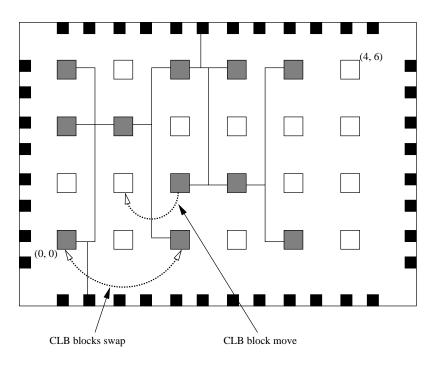

| 17 | Example of implemented design considered as taken/free CLB                       |    |

|    | cells.                                                                           | 62 |

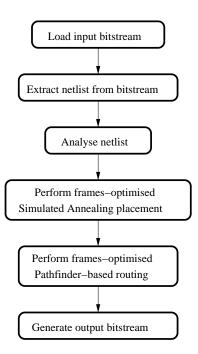

| 18 | Java Placement and Routing framework data flow.                                  | 64 |

| 19 | Pseudo-code of a simulated annealing placer from                                 | 65 |

|    |                                                                                  |    |

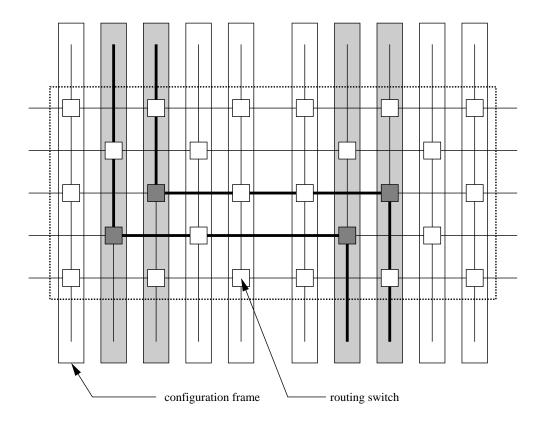

| 20 | Pseudo–code of the Pathfinder routing algorithm                 | 68  |

|----|-----------------------------------------------------------------|-----|

| 21 | Routing implementation and its impact on configuration data     |     |

|    | content                                                         | 71  |

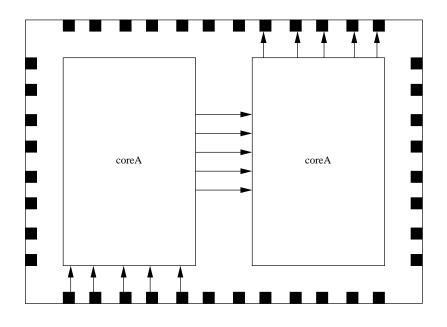

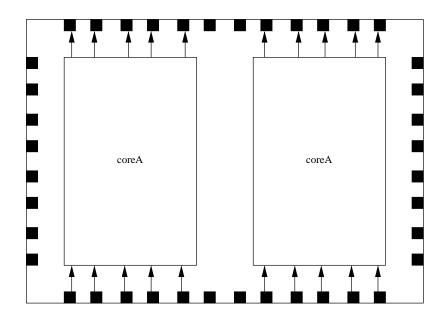

| 22 | Example of serial cores implementation: coreA_chain_x2          | 73  |

| 23 | Example of parallel cores implementation: coreA_coreA.          | 74  |

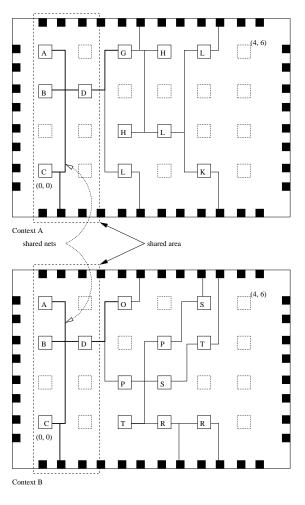

| 24 | Placement of the design using shared and non-shared area        |     |

|    | approach                                                        | 80  |

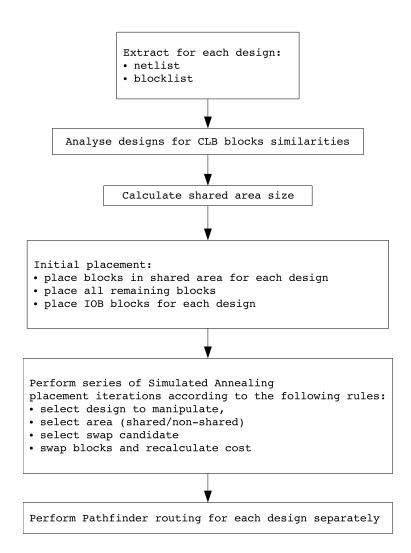

| 25 | Simultaneous Multi–Design Placement and Routing – Design        |     |

|    | Flow                                                            | 88  |

|    |                                                                 |     |

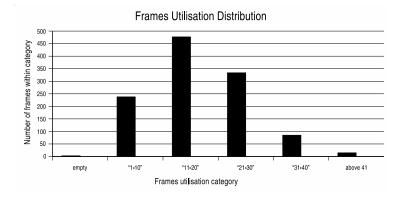

| 26 | Frames utilisation for a design implementation occupying $45\%$ |     |

|    | of device CLBs.                                                 | 96  |

| 27 | b04 Placement Results                                           | 97  |

| 28 | Example of placement result with modified cost function used.   | 100 |

| 29 | Example of placement with next step move resulting in net       |     |

|    | wirelength penalty.                                             | 101 |

| 30 | Example of routing search and its impact on bitstreams size.    | 103 |

| 31 | Example of routing search and its impact on bitstreams size.    | 104 |

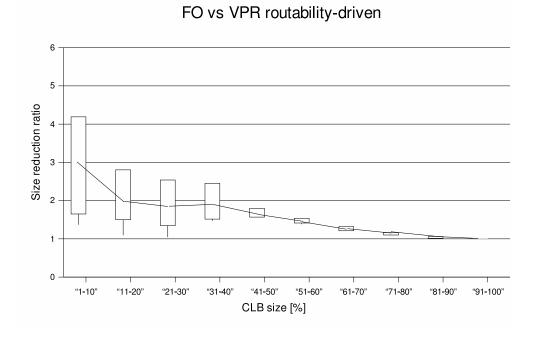

| 32 | Size Reduction Ratio: FO vs STD routability–driven P&R          | 105 |

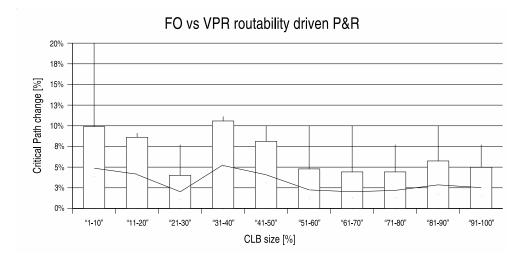

| 33 | Critical Path:FO vs STD routability–driven P&R                  | 106 |

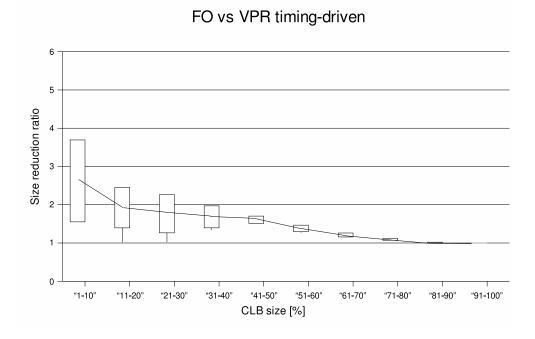

| 34 | Size Reduction Ratio: FO timing–driven vs STD timing–driven     |     |

|    | P&R                                                             | 107 |

| 35 | Critical Path: FO vs STD timing–driven P&R                      | 108 |

| 36 | Placement result for fixed and floating pins: $\#$ – used IO    |     |

|    | block, X – used CLB block.                                      | 109 |

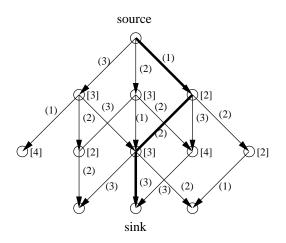

| 37 | Example of SMC P&R performed on two-contexts design             | 115 |

| 38 | Example of Xilinx Virtex single programmable cell               | 121 |

| 39 | Example of proposed configuration interface architecture for    |     |

|    | single Xilinx Virtex programmable cell.                         | 122 |

| 40 | Example of Xilinx Virtex single programmable cell.              | 124 |

# List of Tables

| 1  | Xilinx Virtex FPGA configuration data size summary 61       |

|----|-------------------------------------------------------------|

| 2  | Temperature update schedule                                 |

| 3  | Base costs of different types of routing resource           |

| 4  | FPGA Benchmark Prototypes from ITC99 Benchmark Suite 74     |

| 5  | FPGA Benchmark Prototypes from www.asics.com 75             |

| 6  | FPGA Benchmark Prototypes from www.opencores.com 75         |

| 7  | FPGA Benchmark Prototypes from HLSynth95                    |

| 8  | FPGA Benchmarks Summary – size $1\% - 40\%$                 |

| 9  | FPGA Benchmarks Summary – size $41\% - 99\%$ 93             |

| 10 | FPGA Benchmarks Frames Utilisation Summary – size 1% –      |

|    | 20%                                                         |

| 11 | FPGA Benchmarks Frames Utilisation Summary – size $21\%$ –  |

|    | 60%                                                         |

| 12 | FPGA Benchmarks Frames Utilisation Summary – size $61\%$ –  |

|    | 99%                                                         |

| 13 | Designs similarity summary                                  |

| 14 | FPGA Multi–design benchmarks summary                        |

| 15 | Summary of shared empty and design frames                   |

| 16 | Summary of shared empty and design frames for CLB specified |

|    | frames                                                      |

| 17 | Designs similarity summary                                  |

# List of Abbreviations

| ALU | Arithmetic | Logic | Unit |

|-----|------------|-------|------|

|     |            |       |      |

- ASIC Application Specific Integrated Circuit

- BCT Bitstream Comparison Tool

- CAD Computer Aided Design

- CDS Configuration and Data Store

- CLB Configurable Logic Block

- CMOS Complementary Metal Oxide Silicon

- DLC Dynamic Location Cost

- EDA Electronic Design Automation

- EPROM Erasable Programmable Read Only Memory

- FO P&R Frames Optimised Placement and Routing

- FPGA Field Programmable Gate Array

- HDL Hardware Description Language

- JPR Java Place & Route

- LUT Look-up Table

- MP3 MPEG-1 Audio Layer 3

- MPEG Moving Picture Experts Group

- OTP One Time Programmable

- P&R Placement and Routing

- PCB Printed Circuit Board

- PE Processing Element

- RAM Random Access Memory

- RCU Reconfigurable Control Unit

- RLU Reconfigurable Logic Unit

- RS Reconfigurable System(s)

- RTL Register Transfer Level

- SLU Swappable Logic Unit

- SMC P&R Simultaneous Multi-Context Placement and Routing

- SoC System-on-Chip

- SRAM Static Random Access Memory

- UMTS Universal Mobile Telecommunications System

- VHDL VHSIC HDL

- VLSI Very Large Scale Integration

- VPR Versatile Place & Route

To my parents, family and friends, for their love, patience and support.

# Acknowledgements

This thesis would have not existed without the efforts of many kind individuals. It gives me a great pleasure to acknowledge their contribution here.

I would like to thank my first supervisor, Dr Milan Vasilko, for his advice and encouragement, generous support, and dedication to see this project through to its successful end. I am very grateful to my second supervisor, Denzil Claremont, for his help, constructive criticism and support on this project.

I would like to thank Dr Jon Cobb for supervising the project in its final stage, especially for his support and dedication towards the successful outcome. I would also like to thank Dr Glyn Hadley for his constructive comments.

Special thanks to Professor Jim Roach and the rest of the management team of the School of Design, Engineering & Computing who have provided generous support throughout my studies.

I am grateful to my past and present colleagues, Petr Voleš, Periklis Chatzimisios, Pi Huang, Adam Polus and many others for their friendship, help and an excellent working environment they have provided over the years.

My work on this research would have never been possible without the support from my family. I am grateful to my parents for their continuing support and encouragement in my pursuit of the university studies and the scientific career.

# Declaration

This thesis contains the original work of the author except where otherwise indicated.

# Chapter 1

# Introduction

In recent years, Field Programmable Gate Arrays (FPGAs) have become one of the most popular implementation technologies for digital circuits. Initially, being just a mesh of programmable logic units and interconnections, they have rapidly evolved to become complex System–on–Chip (SoC) solutions offering dedicated processing, storage and communication blocks to satisfy an ever increasing demand for configurable platforms that can be realised with minimum time to market.

The benefits gained from using FPGAs have been demonstrated across different, often computationally heavy application domains:

Various video processing algorithms have been successfully implemented in FPGAs, (Kulmala et al. (2006); Note et al. (2006); Agostini et al. (2006); Gorgon et al. (2005); Hormati et al. (2008), Kirischian et al. (2008)) often outperforming purely software implementations. A video decoder presented by Mignolet et al. (2003) implemented on reconfigurable hardware, was four times faster than its software implementation.

FPGAs have also proven to be an efficient platform for various image processing algorithms, (Garcia and Navarro (2006); Fahmy et al. (2006); Fahmy et al. (2005); Canto et al. (2009)) especially for the ever increasing image resolutions, and the growing popularity of image recognition based systems.

The wireless communications application domain has also benefited from using FPGAs (Ahmed and Arslan (2006); Berthelot et al. (2006); Herrero et al. (2006); Esquiagola et al. (2005); Subramanian et al. (2009); Vogt and Wehn (2008)) to efficiently implement a variety of communication modules.

Examples from Mentens et al. (2006); Michalski and Buell (2006), Legat et al. (2009), Glas et al. (2008) and Huffmire et al. (2008) show that data security and cryptology have successfully used FPGAs in order to provide data security.

Yamaguchi et al. (2002) present results from using FPGAs in Reconfigurable Systems (RS) for a high–speed homologycal search. Their study found that the hardware approach was 330 times faster than an equivalent algorithm optimised for software implementation. Other examples from Arteaga et al. (2008), Koch et al. (2009) and Vogt and Wehn (2008) show, that FPGAs offer better performance for many algorithms previously reserved for microcontrollers.

As SRAM-based FPGAs can be programmed to perform different functionalities, they can also support reconfiguration, where the same hardware infrastructure can be reused to perform different functionality at different times. For this reason SRAM-based FPGA technologies can be considered as Reconfigurable Systems.

### **1.1** The Demand for Reconfigurable Systems

The demand for reconfigurable digital hardware is increasing as manufacturers realise the benefits of reconfiguration, for example:

- Increased functionality without additional hardware.

- Dynamic modification and upgrading of systems with no or minimal

system downtime.

- Realisation of adaptive systems.

- Remote hardware upgrade.

Several approaches have been proposed for reconfigurable systems. A Seamless Communication Platform presented in Vasilko et al. (2001) describes a multi-standard communication system with 'over the air' reconfiguration. Reconfiguration provides platform adaptability to different communication protocols and data coding requirements. Other examples of platforms for reconfigurable designs have been described by Rissa and Niittylahti (2000), Sedcole et al. (2003) and Marescaux et al. (2003).

Wireless communication is a good example of an application area that can benefit from reconfigurable functionality. At the present time, a change in communication protocol or introduction of a new network service often necessitates a user purchasing an upgraded device that supports new protocols. With reconfigurable devices an upgrade can be done in milliseconds (Rana et al., 2009) that is transparent to the user. Examples presented by Herrero et al. (2006), Ahmed and Arslan (2006), Subramanian et al. (2009) and Vogt and Wehn (2008) show that FPGAs can satisfy performance requirements specified by the wireless communication domain.

Apart from end-user devices, mobile base station or satellite transmission systems can also benefit from dynamic hardware reconfiguration. New network services can be introduced rapidly without expensive modifications to network infrastructure. It is especially important in satellite systems, where physical modification of existing satellites in space is usually protracted and costly. With reconfigurable hardware on board, a satellite can be reprogrammed from the control centre to provide new protocols and services. Examples presented by Vladimirova and Wu (2007) and Fiethe et al. (2007)

Figure 1: Example of a multi–context design using a single reconfigurable platform.

show that FPGAs can satisfy performance requirements specified by the satellite communication domain.

Another application area of notable interest is multimedia portable devices. Problems have emerged in relation to the variety of data coding/decoding methods and lack of well established standards. Consequently, many devices are limited in respect of the data protocols they can support. Extending support for new data protocols requires hardware modifications which cannot be done through software.

The example a smartphone implemented on FPGA-based reconfigurable system has been presented on Figure 1.

Single context presented on the Figure 1 refers to a portion of configuration data required to program FPGA to perform desired functionality. It is an equivalent of a single application loaded to the smartphone to switch it into desired functionality (e.g. multimedia player, GPS receiver, etc.).

In many situations reconfiguration of system functionality on a scale of a milliseconds (Resano et al., 2008) would not impose a significant burden on system usability and further improvement is not justified. However, in specific application areas, such as, reconfigurable computing, minimising reconfiguration delay is essential to maximise throughput. For example, real time image processing requires a sequence of processing operations applied in parallel to image blocks. In this type of application optimal throughput is achieved if the images are stored locally in the processing matrix and local hardware reconfigured at each processing step. This overcomes the delay imposed by conventional hardware or sequential processors in moving large amounts of data between different elements of the functional architecture e.g. memory swapping. Moreover, minimalisation of data transfers can lead to significant reduction in power consumption. An example presented by Wang et al. (2006) showed that FPGA dynamic power consumption can be reduced when a modified set of design constrains is used at FPGA placement and routing.

Smit et al. (2002) identified the potential for dynamically reconfigurable mobile communication systems that operate in differing communication environments. In this type of application, additional functionality is limited by the requirement to minimise the physical size of the system to ensure portability and low battery power consumption. By using reconfigurable techniques the system functionality can be extended without adversely affecting these requirements. Similar arguments are presented by Helmschmidt et al. (2003) in their consideration of the realisation of the UMTS rake receiver.

Examples from different application domains illustrate the benefits of using dynamically reconfigurable hardware. An FPGA–based implementation of public–key cryptography algorithm developed by Mazzeo et al. (2003) benefited from a reduced design area and significantly increased performance. Gause et al. (2000) presented two reconfigurable design approaches for two–dimensional Shape–Adaptive Discrete Cosine Transform: one static where configuration does not change during algorithm execution and the second with dynamic reconfiguration enabled. They concluded that the dynamic approach significantly reduced the required FPGA are utilisation, however it was noted reconfiguration latency overhead did not significantly improve. Vissers (2003) describes parallel processing architectures as a network of ALU–like structures with a corresponding set of instructions and recognises the opportunity for rapid dynamic reconfiguration and instruction multiplexing.

## 1.2 Limitations of Reconfigurable Hardware

Although FPGAs offers high performace and flexibility, there are a number of limitations that have prevented them from being widely exploited as reconfigurable systems. Rana et al. (2009) addressed reconfiguration latency – time required to switch configuration – as the key issue undermining performance improvements. As modern FPGAs configuration files size is of MBytes due to their complexity it adds a significant reconfiguration overhead. This impose reconfiguration latency and data storage penalty especially in multi-context designs.

Furthermore, configuration data size becomes an issue especially in battery operated, mobile devices, where configuration data storage and its transfer to the FPGA array contribute to the overall power consumption. The significance of this issue has been recently exemplified by the rapid increase in portable systems, such as MP3 players and mobile phones.

### **1.3** Design Support For Reconfigurable Systems

Efficient use of reconfigurable hardware could be impossible without design tools. They offer fully automated design flow mostly for a single content solutions, able to satisfy variety of design goals, like: routability, meeting timing constraints or power consumption requirements. Typically designs for FPGAs have been described using Hardware Description Language (HDL), proven to be an efficient way to describe hardware. However such an approach is technology dependant.

Multi-context design as presented in Figure 1 can be processed using currently available design tools as a set of individual contexts. However such an approach is unable to benefit from any configuration overlapping mainly because each context is processed separately. Lack of feasible tools for efficient multi-context design has been addressed by Canto et al. (2009).

### **1.4** Scope and Objectives

This thesis evaluates the problem of placement and routing (P&R) for reconfigurable system. The reason to focus on placement and routing comes from the fact, that FPGA configuration data content depends on P&R results. Analysis of the current state of design tools for reconfigurable systems presented in Sections 1.1 through 1.3 allows a statement of the principal aim of the thesis which is the development and characterisation of novel placement and routing strategies for FPGAs that reduce reconfiguration latency and minimise reconfiguration data storage requirements.

The principal objective is to develop a method of minimising configuration data size by re–using parts of configuration data from previously loaded contexts. Novel algorithms will be developed and characterised for representative design applications. The results will be analysed to establish if generalised design rules can be established.

Partial result of this research inluding author's novel placement and routing approach has been published in (Stepien and Vasilko, 2006).

### 1.5 Thesis outline

The current chapter presents an introduction to the field of research and identifies the principal aim of the research project. Chapter 2 provides a critical review of related literature and relevant background information on reconfigurable systems. Evaluation of state-ofthe-art hardware, design methodologies, tools and conceptual approaches have been presented. Several technological approaches to reconfigurable systems together with reconfigurable logic architecture have been examined together with reconfiguration methods in order to demonstrate how the technology-specific features influence the design considerations during reconfigurable system design.

Chapter 3 discusses the methodology used to achieve design goals. It describes details about development framework, testing environment and quality measures used to evaluate the novel placement and routing algorithms. The benchmarking tests used to validate the solutions are also discussed.

Chapter 4 discusses the development of a novel bitstream size reduction methodology for placement and routing of a single context design and its optimisation. It describes how a configuration architecture interface can be incorporated into the placement and routing stage in order to address design goals. Critical evaluation of experimental results has also been presented in this chapter.

Chapter 5 discusses the enhancements introduced for a novel simultaneous multi-context placement and routing methodology. Details of configuration data sharing and its impact on the quality of delivered placement and routing results are also discussed there together with their impact on different FPGA technologies.

Chapter 6 presents the conclusions of the study with the directions of further research.

# Chapter 2

# Literature review

This chapter provides critical review of reconfigurable systems focusing on FPGAs as a leading technology. To describe the complexity of configuration bottleneck problem FPGA technologies have been discussed leading to the critical evaluation of methodologies used to improve reconfiguration. This chapter also provides critical evaluation of FPGA Computer Aided Design (CAD) tools with a focus on reconfiguration improvement.

### 2.1 Reconfigurable System Definition

Reconfigurable systems combine features previously existing individually in either software or hardware systems. Consequently, they provide the flexibility of processor-based software systems with performance approaching that of custom hardware circuits (Shirazi et al., 2000). Typical RS architecture contains a Reconfigurable Logic Unit (RLU), Reconfiguration Controller Unit (RCU), and Configuration Data Store (CDS). The RCU manages the RLU reconfiguration. Typically, the RCU is implemented as a micro-controller or microprocessor. It operates the task of reconfiguration control as well as data transfers to and from RLU. Sometimes, the RCU can be an integral part of the RLU. The CDS unit provides memory for configuration data and application specific data. It can be organised as two separate memory blocks (one for each type of data) or one single memory block shared between configuration and application specific data.

#### 2.2 Reconfigurable Systems Implementation

In the past reconfigurable system required several components: microcontroller, FPGA, DSP, storage. With submicron technology currently available FPGAs from Xilinx, Altera or Actel contain not only the array of configurable blocks but also dedicated microcontroller, DSP, storage and high-speed I/O interace (Xilinx, 2009b; Canto et al., 2009; Lewis et al., 2009; Actel, 2009).

There has been considerable research into possible reconfigurable computing architectures. Alternatives range from systems constructed using standard FPGAs to systems constructed using custom-designed chips. Some technologies like Xilinx XC6200 (Brebner, 1996; Luk et al., 1996; Brebner, 1997a) were introduced to support research on reconfiguration. A review on existing RS architecture approaches by Hauck and DeHon (2008) include discussion of a range of research and commercial technologies including Garp, PipeRench, RaPiD, Chimaera together with FPGA-based PAM, VCC, Splash, Prism and XC6200 architectures.

The variety of hardware solutions arises from the fact, that there is no single universal architecture that fulfils requirements of different applications. SoC has become very application specific in terms of size, available resources and reconfiguration technique, in order to avoid penalties in design speed and efficiency.

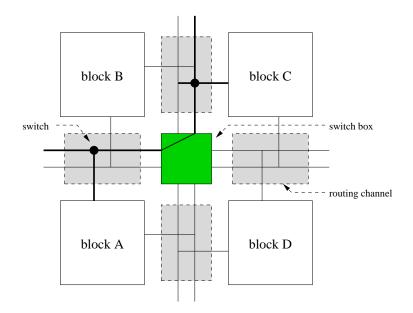

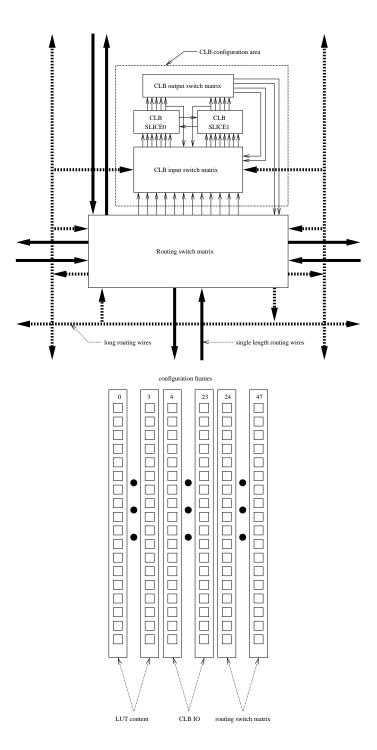

Figure 2: Example of island-style configurable logic architecture based on Betz (1999).

### 2.3 FPGA Architecture

The popularity of static RAM-based technology pushed forward the development of reconfigurable logic. Modern FPGAs offer not only the equivalent of several millions of logic gates but also dedicated microcontrollers, DSP modules, storage and high-speed I/O interface able to accommodate very complex digital designs (Xilinx, 2009b; Canto et al., 2009; Lewis et al., 2009; Actel, 2009).

A typical example of reconfigurable logic architecture is presented in Figure 2. It contains logic blocks (for logic functions) surrounded by the routing wires to provide connections between logic blocks. Wires are connected together via configurable switches controlled by individual memory cells. During the configuration process appropriate switches are set into on/off position to provide connectivity between logic blocks.

As has been described in Betz et al. (1999) all FPGAs are composed of three fundamental components: logic blocks, I/O blocks and programmable routing. A circuit is implemented in an FPGA by programming each of the logic blocks to hold a portion of a circuit's functionality, and each of the I/O blocks to provide connectivity with the PCB. The programmable routing is configured to provide necessary connections between logic blocks and I/O blocks.

#### 2.3.1 FPGA Programming Technologies

According to Betz et al. (1999) there are three different approaches to making an FPGA programmable:

- SRAM cells, controlling pass transistors, multiplexers and tri–state buffers.

- Antifuses.

- Floating gate devices.

While antifuse and floating gate devices represent OTP class of devices, SRAM–based FPGAs became the most popular reconfigurable technology used today.

#### 2.3.2 FPGA Logic Block Architecture

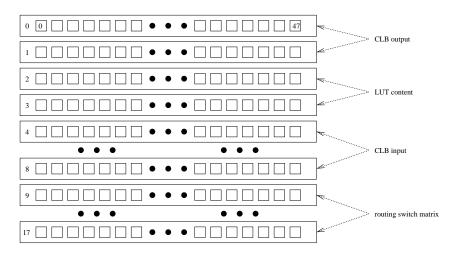

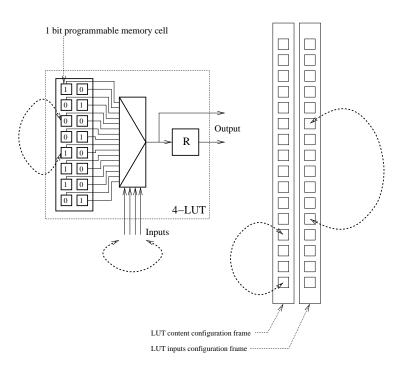

The complexity of logic block used in an FPGA is a trade-off between flexibility, performance and has an impact of reconfiguration latency. While many different logic blocks have been used in FPGAs, most commercial FPGAs use logic blocks based on a look-up table (LUT) (Xilinx, 2009b; Canto et al., 2009; Lewis et al., 2009; Actel, 2009). An example of a LUT-based logic block is presented in Figure 3.

LUT example presented in Figure 3 contains 16 to 1 demultiplexer controlled by four LUT inputs. Depending on combination of LUT inputs selected memory cell is connected to the LUT output. Four bit LUT can perform any four input combinatorial function. Output register R is used to implement sequential logic functions. LUT inputs resolution has been

Figure 3: FPGA logic block with 4-input LUT and register.

investigated by various research groups to establish the optimal logic structure. These studies identified a trade-off between area efficiency and the number of LUT inputs. Eventually, the four input LUT became a standard for commercial FPGAs, although recently with silicon technology going into deep-submicron area 6-input LUTs have been used Xilinx (2009b).

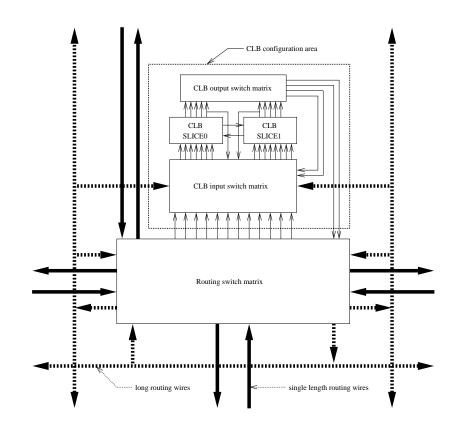

In most of the modern FPGAs LUTs are grouped into clusters in order to host more complex functions inside a single logic block. Often LUTs within a single logic block are locally interconnected to enable them to host more complex functions. In Xilinx Virtex-6 4 LUTs form a slice and 2 slices are grouped into a single Configurable Logic Blocks (CLB) (Xilinx, 2001).

#### 2.3.3 FPGA Routing Architecture

According to (Betz et al., 1999) FPGAs can be classified by routing architecture into the following groups:

• Island–style.

Figure 4: Example of island–style routing based FPGA based on Hauck (2008).

- Row-based.

- Hierarchical.

Island-style routing architecture where a logic block is surrounded by routing resources, can be found in Xilinx and Lucent devices (Xilinx, 2001; Xilinx, 2009b), while Actel's devices are row-based (Actel, 2009), and Altera's devices are based on hierarchical routing architecture (Lewis et al., 2009).

Island–style routing architecture is the most popular approach and is widely employed in commercial FPGAs and research devices. An example of an island–style routing architecture based FPGA has been presented in Figure 4.

As indicated in Figure 4 routing resources are grouped into channels spanning horizontally and vertically alongside logic block locations. Basic routing resources of unit length (i.e. they terminate at the next block location) are used to provide connectivity between logic blocks. Longer connections can be built-up using a combination of single length routing wires, or long wires (spanning more than a single logic block), or a mixture of both, depending on the distance between logic blocks to be connected.

### 2.4 Design Automation

The advent of complex configurable devices with more than a million logic gates, made manual circuit design impractical, if systems were to be realised within the time constraints imposed by market forces. To support the design process, numerous design automation tools and methodologies have been proposed.

## 2.4.1 Design Techniques for One Time Programmable Systems

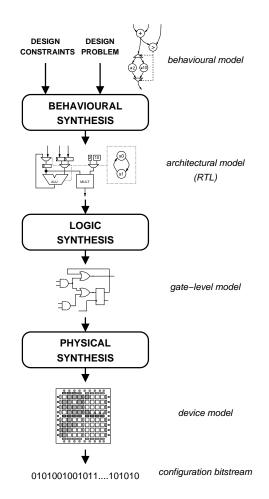

One Time Programmable (OTP) systems refer to the case when the configuration is loaded at startup and it does not change while the system is active. Single context programmed FPGA is a good example of OTP system. The methodology described in this section describes the design automation associated with this type of architecture. It is included as a basis for understanding several of the challenges associated with the current study. Figure 5 presents the typical design flow for non-reconfigurable system.

During behavioural synthesis an abstract behavioural design model is translated into one of several possible architectural design models, whilst attempting to meet the stipulated design constraints. An architectural design model is often referred to as a 'register-transfer level' (RTL) architecture, because it indicates data transfers between register blocks (Vasilko, 2000a). Subsequently, a logic synthesis process translates the RTL architecture description into a gate-level architecture resulting in a gate and

Figure 5: Typical Design Flow for configurable systems based on Vasilko (2000a).

interconnection netlist. This description is generic and a technology mapping process is necessary to map the gate–level netlist onto a specific target technology. The last process is known as the placement and routing (P&R) stage and involves placement of the target technology cells and their routing.

Collectively the steps outlined above form the Electronic Design Automation (EDA) process. Many EDA algorithms and methodologies have been proposed for automatic translation between the various design abstraction levels. For detailed information on these techniques the reader is referred to the literature, Gajski et al. (1992); Sherwani (1995); Gerez (1999) offer comprehensive discussion on these topics.

#### 2.5 Configuration Interface Architecture

Configuration architecture is the underlying physical circuitry that loads the configuration data onto the chip and stores it at the correct location. Configuration architectures can range from a simple serial shift chain to addressable structures that can manipulate configuration information after it is loaded (Hauck and DeHon, 2008).

The process of FPGA configuration is a two stage process involving data transfer from external memory to the FPGA and data distribution to each programmable resource on the chip. The efficiency of the method used to transfer and distribute configuration data determines reconfiguration performance.

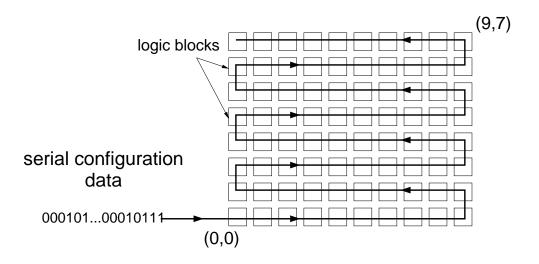

#### 2.5.1 Serial Configuration Data Distribution

The simplest way to manage configuration memory cells in the FPGA is to group them into a single shift–register spanning across entire chip. Data are loaded serially to this register. Once data loading is completed configuration can be activated. Example of serial configuration interface is presented in

Figure 6: Example of Serial Configuration Data Interface.

Figure 6.

Serial configuration approach is quite fast when the entire chip needs to be reconfigured. It is also silicon area efficient due to minimal resources having to be dedicated to control configuration process. However, in situations where only a part of the configuration needs to be changed, entire chip has to be reconfigured due to the constraints of the configuration interface architecture. The Xilinx XC4000 family is an example of this type and incorporates a single serial configuration data distribution interface (Xilinx, 1999).

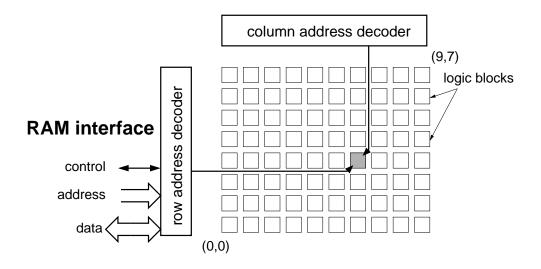

#### 2.5.2 Parallel Configuration Data Distribution

The need for a faster and more direct access to the FPGA configuration registers was identified by Kean (1988). In response, parallel configuration data interfaces were implemented by Xilinx in their XC6200 family. With a memory like distribution architecture, single routing switches became directly accessible, and the configuration could be changed without the need to reconfigure other parts of the device. However, a parallel interface requires much more robust circuitry and is still too slow in many applications where a significant portion of the FPGA needs to be reconfigured. An example of

Figure 7: Example of Parallel Configuration Data Interface.

a parallel configuration data interface is presented in the Figure 7.

### 2.6 Support for Reconfiguration

#### 2.6.1 Partial Reconfiguration

During the early development of FPGAs, reconfiguration was performed at start-up only. Consequently, the serial configuration data interface was a very convenient solution due to its simplicity. With further development of reconfigurable computing, demand for the capability to reconfigure parts of FPGA while other parts continue to operate (dynamic reconfiguration) increased. Lysaght and Dunlop (1994) classify an FPGA as dynamically reconfigurable if it can be partially reconfigured while active. To achieve partial reconfiguration capability, configuration data has been organised into clusters each controlling different parts of the device. Such an approach, allows reconfiguration of a part of a FPGA without interfering with other previously implemented or operational elements of the design.

Figure 8: Multiple–context configuration memory from Vasilko (2000a).

#### 2.6.2 Reconfiguration Latency

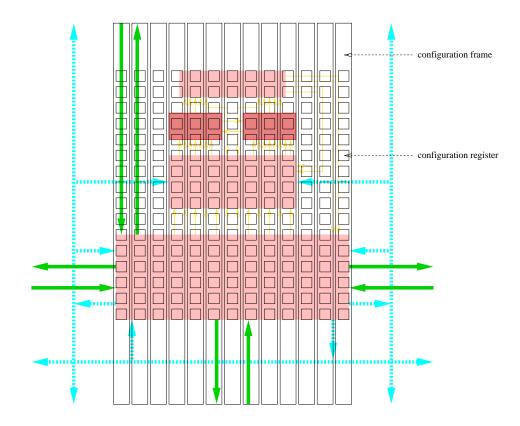

Different reconfiguration mechanisms demonstrate a tradeoff between the configuration throughput and the area overhead required for the implementation of the reconfiguration subsystem. The time needed for the configuration of a design module will vary with the technology. For partially reconfigurable technologies, the required configuration time will also vary with the current contents of the configuration memory in terms of number of frames which need to be reloaded. A frame in this context denotes the smallest sub–division of the device that can be independently reconfigured.

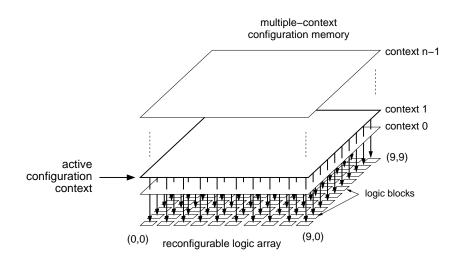

To accelerate the speed of reconfiguration, a cascade technique involving the connection of several configuration cells to one configurable resource was proposed by Brown et al. (1994) and later refined by Trimberger et al. (1997). These systems provide a configuration memory containing more than one configuration data store so that multiple–contexts can be preloaded. The configuration memory for each context is termed a context layer as presented on Figure 1 in section 1.3. Once the configuration data has been preloaded into the context layers, the desired configuration can be activated by selecting the appropriate configuration cells. This process is illustrated in Figure 8. The main advantage of this approach is in the speed of reconfiguration. In current technologies entire device configurations can be changed within a few nanoseconds (Vasilko, 2000a). However, fast reconfiguration is achieved at the expense of the large silicon area overhead required for the configuration context memory and its control logic. Power consumption during reconfiguration is also difficult to estimate, which is an important requirement in the design of multi-function portable devices (Trimberger et al., 1997).

Vasilko and Ait-Boudaoud (1996b), investigated an alternate approach to fast reconfiguration which exploited integrated optoelectronics on silicon. Embedded photo-detectors can be used to configure switches and logic block contents instead of memory cells. Such an approach can benefit from faster reconfiguration without the overheads associated with the multi-context approach previously described. However, the ability to integrate high density optoelectronic detectors on silicon remains a challenge and commercial realisation of optically reconfigured FPGAs has not yet materialised.

Another basic approach to resolving the reconfiguration problem is to reduce the amount of data required to configure an FPGA. Modern FPGA architecture offers millions of simple logic blocks to host all sorts of algorithms. To provide connectivity between these logic blocks routing resources are also increasing exponentially. This gives the designer freedom and flexibility, but comes at the price of an increasing the amount of configuration data that needs to be loaded into an FPGA. For example, a typical configuration data file for the Xilinx XCV1000 which offers the equivalent of one million logic gates requires about 770kB of configuration data. Whilst the quantity of data is not high by today's standards the time to load this data serially even at the highest throughput rates is on the order of milliseconds. This is too slow for reconfigurable computing applications where reconfigurations times on the order of a few nanoseconds are required to sustain typical programme execution and data throughput rates.

Several approaches have been proposed to minimise configuration data

size. Dyer et al. (2002) proposed an architecture in which some of the routing, particularly of data buses is fixed. Thus only a part of the routing switches can be reconfigured which significantly decreases configuration data size.

An alternate approach utilises a different architectural paradigm, where logic blocks are much more complex structures e.g. PACT XPP Technologies (2003). This type of architecture decreases the level of flexibility offered by an FPGA although it benefits from a faster reconfiguration time and reduced configuration data size.

## 2.7 Dynamic Reconfiguration Implementation

The technique of partial reconfiguration subsequently led to the concept of dynamically reconfigurable systems. According to Lysaght and Dunlop (1994), an FPGA is classified as dynamically reconfigurable if it can be partially reconfigured whilst active. With Internal Configuration Access Port (ICAP) introduced on Xilinx Virtex-II FPGAs fabric can be reprogrammed by an internal microcontroller (Eto, 2007). This feature pushed forward research on fault-tolerant and self-reconfiguring design methodologies described in details in (Legat et al., 2009; Sterpone et al., 2008; Pilotto et al., 2008; Hu et al., 2008).

## 2.8 Design Techniques for Reconfigurable Systems

The introduction of reconfigurable systems brought a whole new set of challenges into design automation. The difficulties with the design of reconfigurable systems have been highlighted by Hadley and Hutchings (1995). As modern FPGAs contain a mixture of programmable hardware and microcontrollers (Hadley and Hutchings, 1995) emerged better support of hardware/software design tools.

## 2.8.1 Hardware/Software Design

Introduction of microcontrollers as a part of FPGA fabric emerged the need for new tools linking together two different design methodologies for hardware and software.

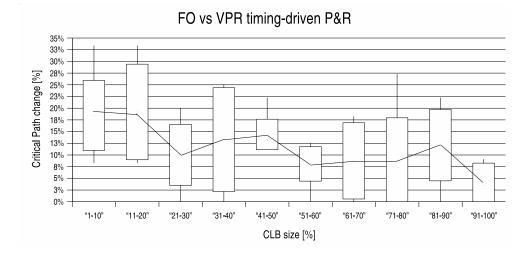

Resano et al. (2008) have developed a hybrid design-time/runtime reconfiguration scheduling heuristic that generates its final schedule at runtime but carries out most computations at design-time. They demonstrated that the PowerPC 405 processor embedded on a FPGA generates a very small runtime penalty while providing almost as good schedule as a full runtime approach.