# APPLICATION OF OBJECT-ORIENTATION TO HDL-BASED DESIGNS

David Cabanis

A thesis submitted in partial fulfilment of the requirements for the degree of

ι

Doctor of Philosophy

**Bournemouth University**

September

2000

~

### DAVID CABANIS APPLICATION OF OBJECT ORIENTATION TO HDL-BASED DESIGN

### ABSTRACT

The increase in the scale of VLSI circuits over the last two decades has been of great importance to the development process. To cope with this evergrowing design complexity, new development techniques and methodologies have been researched and applied. The early 90's have witnessed the uptake of a new kind of design methodology based on Hardware Description Languages (HDL). This methodology has helped to master the possibilities inherent in our ability to manufacture ever-larger designs. However, while HDL based design methodology is sufficient to address today's standard ASIC sizes, it reaches its limits when considering tomorrow's design scales. Already, RISC processor chip descriptions can contain tens of thousands of HDL lines.

Object-Oriented design methodology has recently had a considerable impact in the software design community as it is tightly coupled with the handling of complex systems. Object-Orientation concentrates on data rather than functions since, throughout the design process, data are more stable than functions. Methodologies for both hardware and software have been introduced through the application of HDLs to hardware design. Common design constructs and principles that have proved successful in software language development should therefore be considered in order to assess their suitability for HDLs based designs.

A new methodology was created to emphasise on encapsulation, abstraction and classification of designs, using standard VHDL constructs. This achieves higher levels of modelling along with an improved reusability through design inheritance. The development of extended semantics for integrating Object-Orientation in the VHDL language is described. Comparisons are made between the modelling abilities of the proposed extension and other competing proposals.

A UNIX based Object-Oriented to standard VHDL pre-processor is described along with translation techniques and their issues related to synthesis and simulation. This tool permitted validation of the new design methodology by application to existing design problems.

# TABLE OF CONTENTS

| Abstract                                                                    |          |

|-----------------------------------------------------------------------------|----------|

| Table of Contents                                                           |          |

| List of figures                                                             | iii      |

| LIST OF TABLES                                                              | vi       |

| Acknowledgments                                                             | vii      |

| Glossary                                                                    | viii     |

| Chapter 1: Overview and Requirements Specifications                         | 3        |

| 1.1 Introduction.                                                           |          |

| 1.2 Rationale                                                               |          |

| 1.3 Aims and Objectives                                                     |          |

| 1.4 Taxonomy of Chapters                                                    | 9        |

| Chapter 2: Review of VLSI Design Methods                                    |          |

| 2.1 Introduction.                                                           | 12       |

| 2.2 Schematic Capture Based Methodology                                     | 12       |

| 2.3 Current Hardware System Design Methods and their Limits                 | 19       |

| 2.4 Object-Oriented Methodology for HDL's Based Designs                     |          |

| 2.5 Object Orientation in Standard VHDI                                     | 20       |

| 2.5 Object-Orientation in Standard VHDL<br>2.6 Existing Extension Proposals |          |

| 2.7 Conclusions                                                             | 20<br>66 |

| Chapter 3: Language Design                                                  |          |

| 3.1 Introduction.                                                           |          |

| 3.2 Language Design Decisions                                               |          |

|                                                                             |          |

| 3.3 Language Semantics<br>3.4 Conclusions                                   |          |

| Chapter & Comparative study of propagad extensions                          | 114      |

| Chapter 4: Comparative study of proposed extensions                         | 114      |

| 4.1 Introduction.                                                           | 114      |

| 4.2 Study of the VISTA Proposal                                             |          |

| 4.3 Study of the Active Proposals                                           |          |

| 4.4 Conclusions                                                             |          |

| Chapter 5: Case Study: The Edge Filter Design                               |          |

| 5.1 Introduction                                                            |          |

| 5.2 Overview of Function                                                    |          |

| 5.3 Filter External Interface                                               |          |

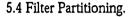

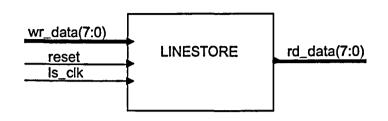

| 5.4 Filter Partitioning.                                                    |          |

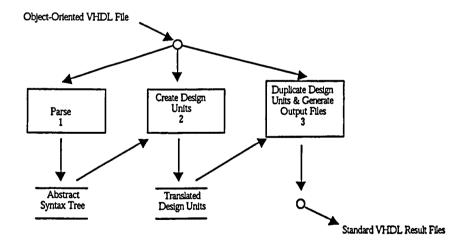

| 5.5 Supporting Class Structure                                              |          |

| 5.6 Edge Filter implementation                                              |          |

| 5.7 Comparative Study                                                       |          |

| 5.8 Conclusions                                                             |          |

| Chapter 6: Preprocessor design                                              |          |

| 6.1 Introduction                                                            |          |

| 6.2 Requirements                                                            |          |

| 6.3 System Design                                                           |          |

| 6.4 Specification of the Translation Mechanism                              |          |

| 6.5 Full Application Example                                                |          |

| · · · · · · · · · · · · · · · · · · ·                                       |          |

| 6.6 Conclusions                                                    | 187 |

|--------------------------------------------------------------------|-----|

| Chapter 7: Overall conclusions and recommendation for further work | 188 |

| References                                                         | 193 |

| Appendix A: Edge filter supporting classes                         | 199 |

| Appendix A-1. Edge Filter Class Structure                          | 199 |

| Appendix A-2. Class Structure Code                                 | 200 |

| Appendix B: Edge filter Code                                       | 205 |

| Appendix B-1. Mult Mask Code Using the Proposed Extension          | 205 |

| Appendix B-2. NS & WE Mask Code Using the Proposed Extension       | 211 |

| Appendix B-3. Line Store Code Using the Proposed Extension         | 216 |

| Appendix B-4. Threshold Mult Code Using the Proposed Extension     | 218 |

| Appendix B-5. Interface Code Using the Proposed Extension          | 221 |

| Appendix B-6. RAM Write Code Using the Proposed Extension          | 225 |

| Appendix B-7. RAM Code Using the Proposed Extension                | 226 |

| Appendix B-8. Filtercore Code Using the Proposed Extension         | 228 |

| Appendix B-9. Mult Mask Code Using RTL VHDL                        | 231 |

| Appendix B-10. NS Mask and WE Mask Code Using RTL VHDL             | 237 |

| Appendix B-11. Line Store Code Using the RTL VHDL                  | 242 |

| Appendix B-12. Threshold Multiplexor Code Using the RTL VHDL       | 245 |

| Appendix B-13. Interface Code Using RTL VHDL                       | 248 |

| Appendix B-14. RAM Write Code Using RTL VHDL                       | 252 |

| Appendix B-15. RAM Code Using RTL VHDL                             | 254 |

| Appendix B-16. Filtercore Code Using RTL VHDL                      | 256 |

| Appendix B-17. Mask Types Code Using RTL VHDL                      | 259 |

|                                                                    |     |

,

.

# LIST OF FIGURES

| Figure 1-1. Rigid Functional Decomposition.                                                   | 6   |

|-----------------------------------------------------------------------------------------------|-----|

| Figure 2-1. Time Related Cash Flow                                                            | .14 |

| Figure 2-2. Schematic Based Design Capture.                                                   | .15 |

| Figure 2-3 Applications of Abstraction Levels.                                                | .17 |

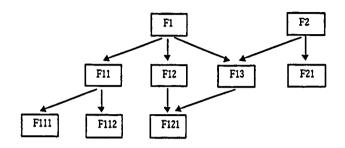

| Figure 2-4. Functional Decomposition.                                                         |     |

| Figure 2-5. Petri Net Description.                                                            |     |

| Figure 2-6. State Machine Graphical Description.                                              | .22 |

| Figure 2-7. Object Based Design Representation.                                               | .27 |

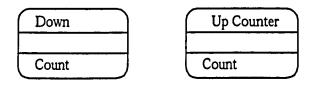

| Figure 2-8. Queues Implementation                                                             | .28 |

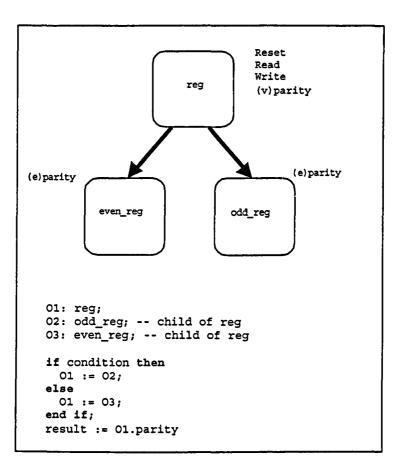

| Figure 2-8. Queues Implementation.<br>Figure 2-9. Algorithmic Description of the Register ADT | .33 |

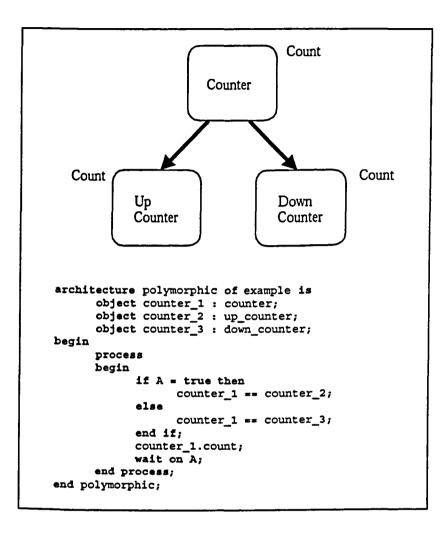

| Figure 2-10. Algorithmic Description of the Counter ADT                                       | .33 |

| Figure 2-11. Message Oriented Communication Scheme.                                           | .34 |

| Figure 2-12. Register Code Re-use                                                             | .35 |

| Figure 2-13. Block-Based Design Structure                                                     | .36 |

| Figure 2-14. Use of the VHDL Block Statement                                                  | .38 |

| Figure 2-15. Counter Described Using The 'Abstract Component' Style                           | .39 |

| Figure 2-16. Use of an 'Abstract Component'                                                   | .40 |

| Figure 2-17. Use of a Package for Building Abstract Data Types                                | .43 |

| Figure 2-18. Package, Visibility throughout the Entity/Architecture                           | .44 |

| Figure 2-19. Narrowing the Accessibility of a Package                                         | .44 |

| Figure 2-20. Selective Access to Package Instances                                            | .45 |

| Figure 2-21. Data Structure Inheritance in Standard VHDL                                      |     |

| Figure 2-22. Abstract Data Type with Records                                                  |     |

| Figure 2-23. Abstract Data Type and Inheritance with Records                                  |     |

| Figure 2-24. Inheritance via Component Instantiation                                          |     |

| Figure 2-25. Initial Code for Abstract Data Type Based Component                              |     |

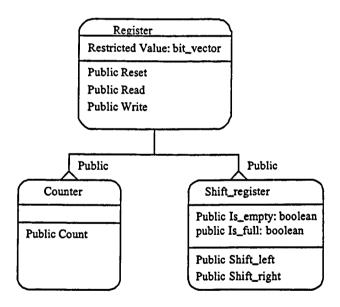

| Figure 2-26. Class Structure for the Counter Abstract Data Type                               | .55 |

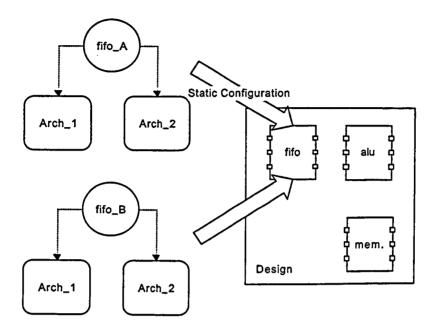

| Figure 2-27. Static Polymorphism through Configuration                                        |     |

| Figure 2-28. Benefits of Dynamic Polymorphism                                                 | .60 |

| Figure 3-1. Class Declaration                                                                 | .85 |

| Figure 3-2. Class Declaration with a Generic Declaration                                      | .86 |

| Figure 3-3. Class Declaration with an interface Declaration                                   | .87 |

| Figure 3-4. Class Declaration with a Generic Declaration                                      | .88 |

| Figure 3-5. Class with Two Methods and an Execution Priority                                  | .92 |

| Figure 3-6. Virtual Class Definition                                                          |     |

| Figure 3.7. Class Definition                                                                  | .97 |

| Figure 3-8. Class Declaration with a Creator Method                                           | .98 |

| Figure 3-9. Dynamic Creation and Removal of an Object                                         | .99 |

| Figure 3-10. Object Instantiation with a Generic Map                                          |     |

| Figure 3-11. Object Instantiation with an Interface Map                                       | 100 |

| Figure 3.12. Declaration of an Array of Objects                                               | 101 |

| Figure 3-13. Non Blocking Object Calls                                                        | 102 |

| Figure 3-14. Object Shallow Copy                                                              | 103 |

| Figure 3-15. Class Encapsulation Levels                                                        | 104   |

|------------------------------------------------------------------------------------------------|-------|

| Figure 3-16. Public Encapsulation during the Inheritance Process                               | . 105 |

| Figure 3-17 Multiple Inheritance Example                                                       | 106   |

| Figure 3-17. Multiple Inheritance Example<br>Figure 3-18. Class Declaration with a Feature Map | 100   |

| Figure 3-10. Debuse with a realise twap                                                        |       |

| Figure 3-19. Polymorphic Behaviour.                                                            | 108   |

| Figure 3-20. Class Using a Type Declared Within a Package                                      | 109   |

| Figure 3-21. Wait Statement Synchronised on a 'stable Attribute                                |       |

| Figure 3-22. Use of Pre Assertions                                                             | 112   |

| Figure 4-1. The EntityObject Abstract Data Type                                                | 115   |

| Figure 4-2. Grouping of Un-related Types in an Array                                           |       |

| Figure 4-3. ADT Declaration in SUAVE/Oldenburg.                                                | 120   |

| Figure 4.4 ADT Declaration in Objective VIIDL and our Proposed                                 | 120   |

| Figure 4-4. ADT Declaration in Objective VHDL and our Proposal                                 |       |

| Figure 4-5. Method Declarations in SUAVE/Oldenburg.                                            |       |

| Figure 4-6. Method Declaration in Objective VHDL.                                              | 121   |

| Figure 4-7. Method Declaration in our Proposal                                                 | 123   |

| Figure 4-8. Abstract Class Declaration in SUAVE                                                | 123   |

| Figure 4-9. Abstract Class Declaration in Objective VHDL.                                      | 124   |

| Figure 4-10. Abstract Class Declaration in our Proposal.                                       |       |

| Figure 4-11. Visible an Non-Visible Declaration in SUAVE                                       | .125  |

| Figure 4-12. Hidden Type Declaration in SUAVE.                                                 | 126   |

| Figure 4-13. Visible and Non Visible Declarations in Objective VHDL.                           | 127   |

| Figure 4.14. Hidden Attribute Declarations in Objective VIIDL                                  | 127   |

| Figure 4-14. Hidden Attribute Declarations in Objective VHDL.                                  |       |

| Figure 4-15. Encapsulation Control in our Proposal.                                            | .128  |

| Figure 4-16. Use of Public Instance Variables in our Proposal.                                 | .129  |

| Figure 4-17. Example Class Structure.                                                          |       |

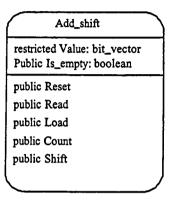

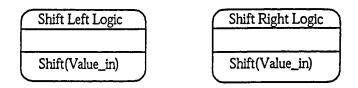

| Figure 4-18. Example Add_shift Class                                                           | .132  |

| Figure 4-19. Feature Mapping in our Proposal.                                                  | .133  |

| Figure 4-20. Inheritance Limits in SUAVE/Oldenburg.                                            | .135  |

| Figure 4-21. Inheritance Limits in Objective VHDL.                                             |       |

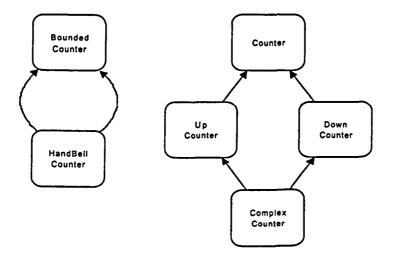

| Figure 4.22. Repeated Inheritance for an Hand-bell Counter                                     |       |

| Figure 4-23. Instantiation in SUAVE/Oldenburg & Objective VHDL                                 |       |

| Figure 4-24. Object Instantiation in our Proposal.                                             |       |

|                                                                                                |       |

| Figure 4-25. Multiple Drivers Assignment in VHDL.                                              |       |

| Figure 4-26. Improper Description of a Counter.                                                |       |

| Figure 4-27. Proper Description of a Counter.                                                  | .141  |

| Figure 4-28. Message Passing in SUAVE/Oldenburg                                                |       |

| Figure 4-29. Message Passing in Objective VHDL                                                 | .146  |

| Figure 4-30. Message Passing in our Proposed Extension.                                        | .147  |

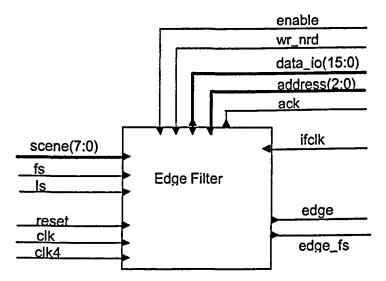

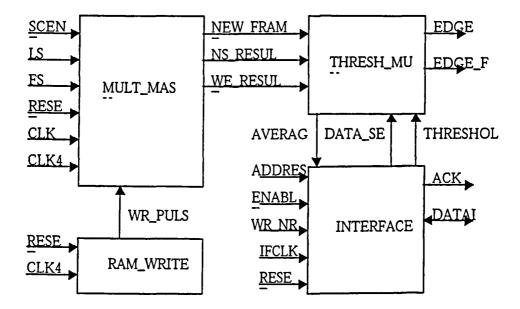

| Figure 5-1. Edge Filter Top Level                                                              | .151  |

| Figure 5-2. Edge Filter Decomposition.                                                         | 152   |

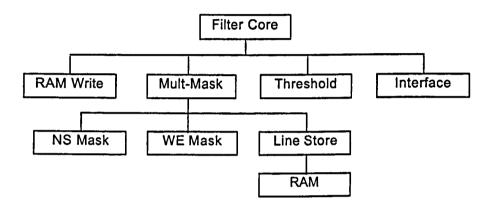

| Figure 5-3. Mult-Mask Top Level                                                                | 153   |

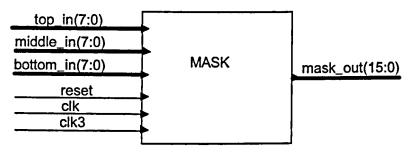

| Figure 5-4. Line-Store Top Level                                                               | 154   |

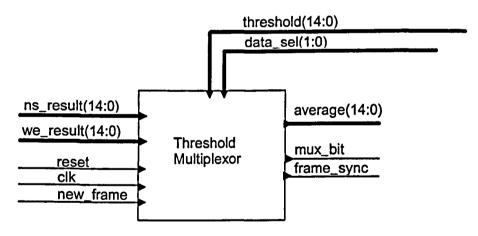

| Figure 5-5 Threshold Multiplayer Ter Level                                                     | 154   |

| Figure 5-5. Threshold Multiplexor Top Level.                                                   | 150   |

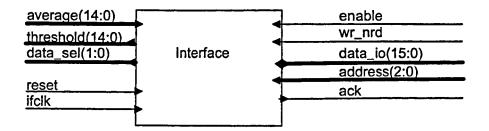

| Figure 5-6. Interface Top Level                                                                | .150  |

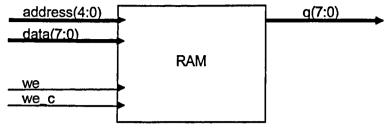

| Figure 5-7. RAM Top Level                                                                      | .157  |

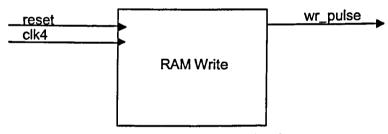

| Figure 5-8. Ram Write Top Level                                                                | .157  |

|                                                                                                |       |

| Figure 5-9. Filtercore Top Level.                        | 158 |

|----------------------------------------------------------|-----|

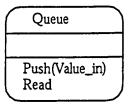

| Figure 6-1. Operation of Pre-Processor                   | 173 |

| Figure 6-2. Class Declaration                            | 174 |

| Figure 6-3. Translated Version of the Class Declaration. | 175 |

| Figure 6-4. Child Class of the 'shift_reg' Class         | 176 |

| Figure 6-5. Translated Version of a Child Class.         |     |

| Figure 6-6. Object-Oriented Method Calls                 |     |

| Figure 6-7. Translation for Method Calls.                | 178 |

| Figure 6-8. Object-Oriented Version of the Example.      | 182 |

| Figure 6-9. Translated Version of the ShiftRightReg.     | 183 |

| Figure 6-10. Translated Version of the ShiftLeftReg.     | 184 |

| Figure 6-11. Translated Version of the BidirShiftReg.    |     |

| Figure 6-12. Translated Version of the Counter.          | 400 |

| 0                                                        |     |

### LIST OF TABLES

| Table 5-1. Threshold Decoding Table Top Level                   | 155 |

|-----------------------------------------------------------------|-----|

| Table 5-2. Detail of Write and Read Operations.                 |     |

| Table 5-3. Case Study Comparative Table                         |     |

| Table 6-1 Translation Process According to Inherited Attributes |     |

•

### ACKNOWLEDGMENTS

This research was sponsored by the School of Design, Engineering and Computing at Bournemouth University and IBM Havant, UK.

The author would like to acknowledge the help and support given by his supervisor Doctor David Long and Nick Weavers.

The author would also like to acknowledge the support of the fellow researchers and members of staff of the School of Design, Engineering and Computing at Bournemouth University.

#### GLOSSARY

ASIC. Stands for Application Specific Integrated Circuit. This is usually used to refer to an integrated circuit (IC) that is designed to implement the functionality required for a popular product as opposed to standard ICs that implement a more diverse function that can be used in wide range of products. An ASIC solution reduces the number of ICs required for a product and so reduces the production cost. ASICs are one of the major growth areas in electronics.

Abstract Data Type. An abstract data type is a type, which defines a set of visibility rules and interfaces for accessing its internal properties. ADTs represent the back-bone of Object-Oriented programming.

Abstraction Level Term used in the latest Hardware Description Languages to indicate the level of details used to describe a design. Commonly, three main levels are specified: Behavioural, Register Transfer, and Structural. The Behavioural level represents the most abstract form of description, mainly focusing on the behaviour of a design. The Register Transfer defines the implementation details of a design. The structural level is mainly used for assembling hierarchical blocks of a design.

Attribute. Also referred as feature, name given to the composing elements of an abstract data type such as access messages and internal instance variables.

**BNF.** Stands for Backus Naur Form. A context-free method for expressing the syntax and structure of a programming language. Used extensively in the IEEE VHDL language reference manual.

**FPGA.** Stands for Field Programmable Gate Array. Also referred as Complex Programmable Logic Devices (CPLD). This is the cost effective alternative to an ASIC for smaller production quantities. FPGAs benefits form a fast design cycle and on site re-programmability due to their static RAM based architecture. FPGA are generally more expensive than ASICs on a unit basis. This is caused by their complex coarse-grained architecture.

**Genericity.** Also referred as tailorability, term used to qualify the level of reusability of a design. A design is said to be generic if it provides the user with a number of modifiable parameter to allow for context sensitive adaptations.

**HDL.** Stands for Hardware Description Language. Depending on their complexity, HDLs will support different levels of abstraction. The latest HDLs languages are based on complex sequential programming languages and allow high abstraction levels systems description. HDLs are used both for simulation and implementation (synthesis) purpose.

**Inheritance.** Inheritance is an important feature of object-orientation. Inheritance provides a mechanism for design reuse by deriving functionality from an already existing one. Inheritance is one of the mechanisms supporting polymorphism.

**Logic Synthesis.** The logic synthesis operation consists in transforming register transfer language description in an optimised set of Boolean equations. The resulting equations are then mapped into ASIC library component primitives following some user-defined constraints (mainly related to execution speed and size of the design). High-level synthesis tools also include a primary operator optimisation stage.

**Object-Orientation**. The object-orientation is a collection of means for organising a description (e.g. specification, implementation). From this perspective, object-orientation may be regarded as a methodology. Two of the most important mechanisms introduced by object-orientation are inheritance and polymorphism. These two techniques when used in disciplined fashion will promote design maintainability and reusability.

**Polymorphism.** Object-oriented mechanism also known as late binding. Polymorphism characterises the dynamic *type* of an element. Polymorphism due to inheritance is often considered as an important contributor to object-orientation.

**Register Transfer.** The register transfer terminology is used to characterise a description's level of abstraction. This level is situated under the behavioural level (also known as executable specifications) and above the gate level (netlist format). The register transfer level description of a system specifies in detail the logic building blocks composing it and their connectivity.

**Simulator**. A simulator can evaluate a system consisting of components described at different levels of abstraction (e.g. a mixture of behavioural, register transfer language, and gate level). The evaluation of each of the system's node status is generally event based. The input stimuli required for the execution of the simulation are often referred as test bench or test harness.

**VHDL** Stands for Very High Speed Integrated Circuit Hardware Description Language. This language was designed by the Institute of Electrical and Electronic Engineers (IEEE), primarily as a specification/simulation language. A subset of this language can be translated into a physical circuit layout by synthesis tools.

**VLSI.** Stands for Very Large Scale Integration. The technology that enables integrated circuits (ICs) containing millions of deep sub-micron transistors to be fabricated.

#### Chapter 1

# OVERVIEW AND REQUIREMENTS SPECIFICATIONS 1.1 Introduction

This thesis describes the research work performed towards the application of the Object-Oriented paradigm to the Very High Speed Integrated Circuit Hardware Description Language VHDL (DASC 1993). This chapter summarises the contents of this thesis through taxonomy of the chapters along with a definition of the project background and objectives.

#### 1.2 Rationale

The rapid advance in integrated circuit technology over the past two decades has driven the need for improved design entry tools. There are a number of advantages to be gained from the introduction of HDLs in ASIC design. Amongst them, is the ability to describe systems at different levels of abstraction: from a structural to behavioural description of the design. This allows faster and more reliable design capture, hence improving time to market. HDL based ASIC designs represents one of the main growth areas in the field of the digital electronics. However, although well suited for today's design sizes, Hardware Description Languages such as Verilog or VHDL already show some limits (Weiss 1994) for handling multi-designer large-sized designs. This is related to the bulk philosophy on which both languages have been built. This research investigates the limits found in the most popular HDLs for handling the concepts of design abstraction, reusability, extendibility and maintainability in an effort to develop a better suited language based on the Object-Oriented paradigm (Khoshafian 1989) (Booch 1991).

The notion for reusability and extendibility are primordial in the design of any application specific integrated circuit since most projects either represent a

cut-down or improved version of existing products. This is mainly motivated by the need to limit development costs for these projects.

As a result, it is crucial to specify and design electronic systems with reuse and maintainability issues in mind.

The two principal Hardware Description Languages (VHDL and Verilog) do not represent the ideal solution for the specification and building of large designs, as both languages are based on the widely used structured and obsolete programming methodology. Although structured programming represented a reliable methodology for designing small to medium sized systems it has long been acknowledged for its limits in the software world. A new hybrid language has therefore been created along with a pre-processor to address those limits. This language is enhanced with a layer of constructs favouring the use of object-oriented techniques for code structuring. Numerous extensions have been proposed by the design community to handle large descriptions (Vista) (Shumacher 1995) (Cabanis 1995) (Ashenden 1997) (Radetzki 1997).

An ideal hybrid language should be an orthogonal extension to an already existing and well-structured language, thus allowing optimal integration within the type system and philosophy of the original language. Furthermore, the new capabilities of the language should allow modern analysis and design methodologies to be used.

With procedural languages such as Verilog or VHDL, a multi-abstraction level paradigm is used to specify, simulate, design and implement a system. The Behavioural Level represents an abstraction of the functionality described during a functional decomposition. Consequently, at this stage of the design process, only functionality issues are addressed. The Register Transfer Level (RTL) also known as Data Flow Level, implements the physical aspects of the required functionality taking into account phenomena such as timing and power consumption along with cost related issues such as the design size. The Gate Level will represent the result of an automated translation of an RTL description into a net list format.

The approach taken in most HDL based designs relies on a functional decomposition stage, followed by a behavioural specification for the functional blocks. The behavioural description is used with a test bench to ensure the consistency and correctness of the design throughout the construction of the system. The same test bench is then used with the RTL and gate level versions of the design as a means to cross-check the functionality during the different stages of the system's development.

For each level of abstraction, designers are required to build an interface in order to adapt the test bench to the abstraction of the information exchanged. The functional blocks interface types are usually different and not compatible from one level of abstraction to the next. The behavioural level will usually maintain user-defined types for interfacing. The register transfer level and gate level will be using more hardware-related types such as "bit" based or "standard logic" based types (either scalar or composite versions).

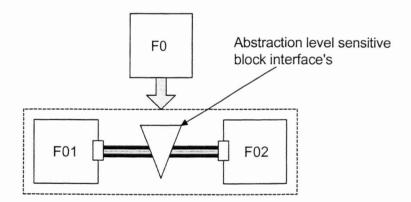

A problem with this approach is that the communication channels used to exchange information throughout functional blocks are often prone to changes during the life of a project. As a result, any minor changes in the system specification will have an important effect on the amount of work required to update the implementation. Furthermore, as can be seen from Figure 1-1. the structure of any functional block is very rigid and often cannot be reused for other applications without requiring significant reengineering effort in terms of design debugging.

Figure 1-1. Rigid Functional Decomposition.

The need for an improved method for modelling is increasing as the size and complexity of new IC's designs steadily grows. On-going work on the subject is being carried out by an IEEE committee (Berger 1995) with the intention of developing a solution for the next generation of HDL. However, the best alternative is not clear, as there is no one solution to address all aspects of current design methodologies' limits. In terms of modelling, a number of issues that should be resolved can be listed. These include:

- Which design methodology ensures better reusability, maintainability and extendibility of hardware designs.

- To what extent a better design methodology could be implemented with already existing HDLs.

- What would be the requirements for the implementation of an improved Hardware Description Language.

- How to maintain a consistent link with already existing designs and CAD tools.

- To what extent reusability could be achieved with a new language when compared to existing HDLs.

- What should be the range of applications of any new language? E.g. specification, simulation, synthesis or formal verification.

Object-Orientation has been used in a number of concurrent processing applications since the encapsulated nature of an object provides a good mechanism for representing independent asynchronous processing units. Consequently, this infers that Object-Oriented modelling might be beneficial for the description of hardware systems.

Pragmatically, there are three main domains in hardware design where the use of Object-Orientation might prove beneficial. Primarily, enabling HDLs to support Object-Oriented constructs would narrow the gap between system analysis and system design. Both stages could be developed around an objectbased methodology, hence, reducing the costly iterations that typically occur between the design stage and the analysis stage. This line of thought is related to the use of abstract interfaces for inter-component communication. For instance, as designs become more complex, it becomes almost mandatory to work at different levels of description (Behavioural, RTL, and Gates) for the different building blocks. As a result this task requires a significant effort in terms of project planning. Different parts of a system will be developed at a different pace using a variety of capture tools and means of verification. In the example of a common design, some parts might be bought from an external supplier (Intellectual Property) with fixed specifications, and interfaces. The level of details for those components will inevitably be low (RTL or Gate) since these models are designed for synthesis. Other hierarchical blocks of the designed system may require a "top-down" approach before getting to the implementation stage. With those blocks, implementation decisions may be delayed until a later stage. As a result, means of abstraction are needed for the overall design capture.

The second benefit of the use of object-orientation is related to the concept of inheritance. The inheritance represents a powerful means for categorising elements of systems and expanding their capabilities by derivation from already existing element attributes. Most modern ASIC designs are based on improved versions of existing designs, inheritance if used with hardware design would simplify the building of the new design and shorten time to market.

The third aspect is related to the modelling of large designs. Historically, software and hardware languages have been improved to further extend their abstraction capabilities. For instance, in the software world, structured languages such as C and Pascal that replaced assembly code have in turn, been replaced by Object-Oriented languages (namely C++ and other implementations of Object-Orientation). A similar analogy can be found in hardware design where gate level design and logic level description languages such as ABEL or PALASM have now been replaced by more abstract languages, namely, Verilog and VHDL.

Although a higher level of abstraction in a design commonly results in a less efficient implementation, the trade-off has proven worthwhile when the time to market, design maintainability and design extendibility represent important criteria.

To some extents, VHDL can be seen as an improved version of the Verilog language for its support for complex data structure, encapsulation and strong typing. If inheritance and polymorphism were to be added to the language to improve its abstraction capabilities, changes would have to be made to the VHDL encapsulation and type mechanisms to cope with the new designs inheritance and dynamic types.

This project focuses on improving the modelling capabilities of the VHDL language by increasing its abstraction level, thereby bringing hardware

modelling to higher grounds. As a result this should be better suited for the building and verification of large reusable designs. To achieve the announced objective, language extensions have been researched and added to the VHDL language with three essential criteria in mind: orthogonality of the new constructs with the existing ones, respect of the VHDL language philosophy (strong type system) and minimal changes to the language. Hardware models based on the new semantics and design methods have been developed, leading to the creation of a demonstration pre-processor tool to prove the validity of the research.

### 1.3 Aims and Objectives

To design a HDL for modelling large reusable hardware/software systems that is compatible with already used languages and proven design methodologies namely VHDL and the Object-Orientation.

To develop models in order to validate the proposed semantics and to illustrate the benefits of object-orientation applied to hardware description languages when dealing with behavioural and register transfer description level.

To create an experimental compiler/pre-processor to evaluate and validate the benefits of the proposed semantics over standard VHDL.

#### 1.4 Taxonomy of Chapters

1.4.1 Chapter 1

This chapter introduces the research work carried out to achieve the project objectives and main issues involved. A brief description of the thesis layout is also given.

### 1.4.2 Chapter 2

An analytical study of the work carried out on design methodologies and proposed solutions to Object-Orientation applied to Hardware Description Languages is carried out in this chapter. This review is based on the material published in a range of software and hardware technical publications, books, journals and conference proceedings.

### 1.4.3 Chapter 3

The definition of the new semantics is described in this chapter along with the motivations for selecting the classification orientation versus other available solutions for achieving Object-Orientation.

### 1.4.4 Chapter 4

This chapter evaluates the validity and superiority of the newly proposed syntactical constructs by comparing our proposed extension to other existing proposals. The comparison uses a common set of benchmarks derived from the language design objectives set in chapter 2.

#### 1.4.5 Chapter 5

This chapter demonstrates the proposed extension abilities for implementing design abstraction, reusability and maintainability. This is done by implementing a real-life application using our proposed extension. In order to contrast the proposed extension with standard VHDL code, the studied design will also be implemented using the VHDL RTL style. The comparison results will be used to draw conclusions on the benefits of our proposed extension over conventional VHDL code.

#### 1.4.6 Chapter 6

This chapter presents the overall conclusion of this thesis. It also makes recommendations for further work and applications for an Object-Oriented Hardware Description Language.

# 1.4.7 Appendix A

This describes an experimental pre-processor that has been developed to demonstrate how a pre-processor handling inheritance, dynamic polymorphism and encapsulation could be developed to support the semantics developed in this thesis.

# 1.4.8 Appendix B

This appendix contains the code for the Object-Oriented description of the supporting classes for the design of the Edge Filter.

# 1.4.9 Appendix C

This holds both the Object-Oriented and RTL Code for the design of the Edge Filter.

#### Chapter 2.

# REVIEW OF VLSI DESIGN METHODS 2.1 Introduction

VLSI design and software engineering are two key areas for which a rise in productivity is needed in the near future. There has been an interesting awareness of similarities in the two fields (Kumar 1993). The willingness to transfer technologies that have proved to be successful from one area to the other became stronger because of the limits of the schematic capture based methodology (Smith 1986), (Wirth 1998), (Shelor 1994). Designers who have experience in both areas have always spontaneously done technology transfer between the two disciplines. Some of the fields where technology transfer has worked successfully are in silicon compilation, in which part, or all of the process of translating a VLSI design concept into mask level layout instruction, has been automated. Like software language translators, which range from assembler to fourth generation languages systems, silicon compilers automate translations. Similarly, the assembling of predefined standard cells on a chip using traditional programming concepts to create a procedural VLSI design methodology has proved to be a success, applying to a VLSI design program, transformation approaches originally developed for software. These conclusive experiments led the designers to assume that a software like capture based methodology could be beneficial to the VLSI design process and to conceive Hardware Description Languages.

The next step hardware designers took in favour of technology transfer was the adoption of software analysis and design methodologies. Although hardware designers valued ASIC design, functional decomposition and structured analysis/ structured design methodologies, the concept of Object-Orientation, originally a software concept, was gradually gaining support within their community. The notion of objects was first introduced in the language Simula (Dahl 1966), designed in the late 1960's. However, Object-Oriented programming did not emerge as a new analysis and programming paradigm until Smalltalk (Goldberg 1989) came along by the end of the 70's. Many Object-Oriented programming languages are widely used today. Although some of them have been designed from scratch, most of them are hybrid languages, that is to say conventional languages with added Object-Oriented concepts. This chapter will examine the limits of the current methods and identify requirements for an improved Hardware Description Language.

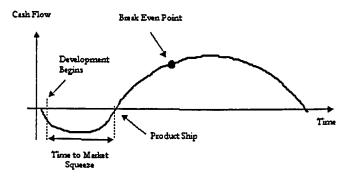

#### 2.2 Schematic Capture Based Methodology

Critical time to market constraints and hardware costs have led ASIC development to rely on efficient design methodologies for decades [Figure 2.1]. Mask design was the first methodology used for the production of LSI designs; it was later replaced by logic level schematic capture. Schematic capture has been the main design entry technique used until the mid-eighties when hardware description languages appeared (Barbacci 1981).

Although the HDL based technique for developing hardware is similar to high level language to develop software, a number of issues have motivated the move from a visual graphical based methodology to a language based one.

Figure 2-1. Time Related Cash Flow.

In a graphical based methodology, some information is provided to infer and clarify the functionality described in the schematic. This information will relate to specific data flow in the circuit, feed back data path, data dependencies or sequential and parallel operations. This means of representing a design is very convenient, as it does not just show how electric components connect but also how they operate. However, as component complexity increases, representing hierarchy via graphical means becomes limited. An example of this limitation can be found with the standard ANSI/IEEE standard symbols such representations are effective for small and limited functionality components but fail to address LSI or VLSI types of components, which are too complex to be represented in an efficient way.

Commonly, hardware designers add a number of indications on a design, such as specific vertical/horizontal alignments (for parallel or sequential executions), a data flow operating from left to right and others [Figure 2.2]. In most cases, a schematic should provide information that can be understood by a person reading it. The interpretation of this information has not been clearly defined and has been adopted by tradition. All these implicit means of giving information do not have their counterpart in language based designs; this justifies the popularity of graphical entry tools as "front ends" to HDL designs. Design tools such as state diagrams, flow diagrams, logic tables and others, support different design entry formalisms.

Figure 2-2. Schematic Based Design Capture.

To overcome this lack of information in HDL designs, run time assertions and inline comments can be used to clarify the code functionality. For example, information regarding the use of a specific architecture or sequential statement such as 'if' or 'case' infers the use of either multiplexor or decoder based structures. Well-commented code can often overcome some schematic shortcomings.

Furthermore, HDL based descriptions free the designer from unnecessary details by abstracting ASIC library components. FPGA designs represent an exception to the rule. Due to their coarse grain architecture: internal features (IO blocks, internal clock buffers, etc.) need to be explicitly inferred to achieve satisfying synthesis results (Xilinx 1997). Ideally these problems should be solved as synthesis tools improve in the same way as for high level language software compilers.

In any kind of engineering construction, the most important factor for productivity is the reuse of prior effort (Keating 1998). This has greater significance in ASIC design, where getting the design right first time is a primary goal and design mistakes can jeopardise a project or increase the cost and shipment time drastically. Consequently, every reuse of well-tested and validated components increases the overall design reliability and reduces the cost and effort required. These factors apply equally to schematic or HDL based design methodology but, the use of the latter maximises its effect. When designers migrate from a schematic environment to a language environment, their motivations are often tied to the needs of creating larger designs within smaller time scales. Therefore the opportunity for reuse of larger designs increases with larger ASICs. To be able to apply design reuse, various elements need to be taken into account: the existence of functionality; what it provides; what it needs; its limitations and whether the level of testing has been thorough enough. Schematic capture does not guarantee the development of reusable parts in terms of genericity. Even though provisions for reuse can be built in, changes in ASIC technology cannot ensure direct mapping across ASIC libraries. Unlike schematic capture, with a HDL based design, a switch from one technology to another is a straightforward

operation, due to the technology independent nature of HDLs, thus preventing design obsolescence.

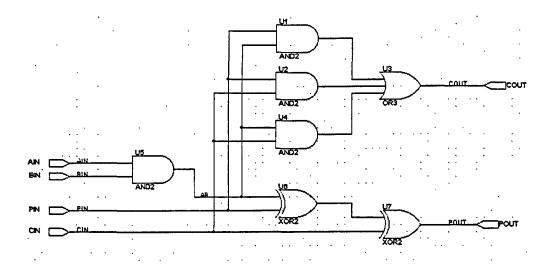

Hardware Description Languages can be classified according to their levels of abstraction (see Figure 2.3). Most of the early HDLs such as CDL (Chu 1965), DDL (Duley 1968), were designed specifically for description at the Register Transfer Level. Today, these languages represent the lowest entry level before the structural level. With these languages, the system had to be described in depth, using rigid expressions to assist the synthesis tools.

Figure 2-3 Applications of Abstraction Levels.

Later HDLs such as ARCHI (Nixon 1986), ADL (Leung 1979), S\*A (Dargupta 1981), ZEUS (Lieber herr 1981) were aimed at micro-architecture level designs. With these HDLs, the description was based around a set of predefined architectures to make the design process easier, but design possibilities were restricted by the rigidity of the predefined architectures. Besides, these languages are not adequate for describing the digital system

design process, as they are often restricted in their ability to support different levels of abstractions.

In recent years, much research has been carried out on Multi-level HDLs. One of the solutions for this problem was to develop a single language that could support a large class of architectures. Some languages which fall into this category are ELLA (Morison 1985), Modlan (Pawlak 1981), UDL/I (Kartsu 1991), Trio (Coen-Porisini 1991), VHDL (DASC 1993) and Verilog (Verilog std 1364-1995). Three levels of description are currently supported by these languages: Structural, Data Flow (or Register Transfer Language) and Behavioural. Although these languages offer an efficient way of modelling and designing digital systems, few of them offer links from system specifications to Register Transfer Level, which represents the closest level to layout. Consequently, the resulting code for a complex ASIC (Application Specific Integrated Circuit) will become large. Apart from these languages, some research has been carried out in the field of specification languages. They are either a formal semantic for specifications such as ESP (Chu 1993), or a syntactic scanning, semantic analysis, interpretation generation and model integration of the English language (Cyre 1989).

Nevertheless, no specification language can be considered complete if it does not support any development techniques for analysis and reasoning. Typically, the phases of a development process include various stages: requirement analysis, design, implementation, test and integration stages. Hardware Description Languages such as VHDL were primarily designed for addressing those aspects; although nowadays VHDL cannot be used for all stages of a design, its use covers most of them. Within one development environment, engineers are able to specify, design and implement a circuit validating each level of the hierarchy via high level VHDL test benches. In comparison, schematic based designs do not allow such abstraction; the highest level often considered is the top-level block diagram. Furthermore, since a VHDL design methodology is language based, this indirectly provides a convenient means of documentation.

VHDL, like most of the modern hardware description languages, is based on a structured programming technique. Structured programming was designed to organise complex programs more efficiently by linking the processing functions to the data structures. The method of functional decomposition characterises the steps that must be taken to reach a particular goal. These steps may be presented by functions that may take arguments in order to deal with data that is shared between the successive steps of the computation. In general, this method is not very good for data hiding. Another problem is that new designers may not be familiar with viewing their problems in terms of computation steps. Also, the method does not result in descriptions that are easy to alter. This leads us to further examine the limitations of current hardware system design methods in order to offer alternatives.

#### 2.3 Current Hardware System Design Methods and their Limits

The choice of analysis and design methods is often motivated by the designers' need to manage design complexity and to keep development and maintenance costs down. Numerous analysis and design methodologies have been used since the 70s, contributing to a better definition of design processes. Besides, there has been an attempt at standardising the system representations used by designers. Electronic engineers successfully use two main methods: Functional Decomposition and System Based Analysis.

Figure 2-4. Functional Decomposition.

Functional decomposition treats one function at a time, and hierarchically decomposes it into a set of sub-functions. This process continues until the decomposition level is low enough to be implemented by a set of simple functions as shown in figure 2-4. This method is based on the principle that a problem can be divided into smaller manageable problems to reduce the complexity of the design. Consequently, the functional decomposition is seen as a simple approach towards achieving a sensible solution. Nevertheless, with this approach, the analysis effort is mainly based on creating design functions at the expense of data consistency. Furthermore, function decomposition rules are not clearly stated and therefore the decomposition hierarchy of a system will vary from one designer to another. Finally, the non-hierarchical interconnections encountered in the design of complex systems (between different taxonomies or within the different levels of the same tree) are difficult to represent with the functional decomposition paradigm.

System based analysis is inspired from the system theory by (Lanffy 1968); the system is seen as a complex and active object. The structural and functional aims of such an object are described at the System Analysis stage. Both Data models and Process models therefore represent the modelling of a system. Design rules are also provided for a better data consistency and process description. This approach appears to be an improvement over the functional

decomposition method. However, in this paradigm, the data and processes description techniques are not closely related.

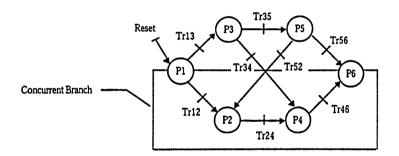

An alternative approach to the system level description is based on graphical methods. Like system based analysis, graphical tools rely on an algorithmic description of the system. One of the most efficient but cumbersome methods is the Petri net description (Gourgand 1993). By using this paradigm, the concurrency within a design, as well as the data exchange protocol, can be expressed in a precise way [Figure 2-5]. As the description gets larger, the Petri net is more likely to make errors when events drive the system to a dead end or an infinite loop. Techniques based on matrix resolutions have been developed to overcome these problems but the description still rapidly becomes unmanageable.

Figure 2-5. Petri Net Description.

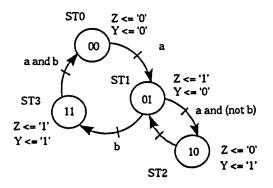

Mixed language and graphical tools based on state diagrams are derived from the Petri net theory. Some languages that fall into this category are SpecCharts (Vahid 1991) and StateChar (Harel 1987). These languages represent an extended way of describing a system's behaviour at the algorithmic level. Nevertheless, the progress in system level description tools research (Kurup 1998) has brought new problems to light. For instance, as the level of abstraction increases, lower level models can no longer be expressed. Conversely, it may not be possible to directly implement expressions in higher abstraction levels onto lower level models.

As a result, engineers commonly use finite [Figure 2-6] or algorithmic state machine descriptions, allowing low level modelling at the expense of abstraction level.

Figure 2-6. State Machine Graphical Description.

In addition to Petri net theory derived descriptions, there has been research reported on system level description using the well supported structured and functional analysis techniques (Lahitis 1991), (Bakowski 1992). These consist of hierarchical data-flow diagrams, which describe the flow of data and control signals inside the system, in response to external stimuli. It provides a system level description that is suitable for synthesis, as the method allows high level representation as well as low level modelling. Furthermore, such methods are based on reasoning techniques for which the designer follows clearly defined steps.

Although the latter techniques seem to be the way ahead for system level synthesis, they soon become inefficient when designs grow in complexity.

With large designs, work is usually allocated among different people. Ideally, designers should not have to know complex details concerning units built or modified by other people, only how the units they are responsible for interact with the rest of the system. However, with methodologies that do not emphasise encapsulation and information hiding, multi-person development team issues are more inclined to occur.

In addition to the design consistency issues, the development cost of large designs is usually very high. The cost of developing could be reduced, if some of the units the system is built from could be taken from already existing systems. Similarly, it would be beneficial if some parts could be reused in future projects. Nevertheless, neither functional decomposition nor System Analysis/ System Design (SA/SD) methods clearly emphasise the reuse and extendibility aspects of a design.

In addition to the discussed design method limits, the building of large systems using the functional decomposition or SA/SD methods do not facilitate the creation of components that closely relate to the application domain. The reason is that design based on such methods identifies two kinds of entities: the data, which are passive and represent the system, and the functions, which manipulate the data.

As a result, the designer of a system written in a procedural language such as Verilog or VHDL will face two alternatives. Either map the problem into a set of functions and define the data structure needed by the functions or map the problem to a set of data and write the functions that transform the input data into output data.

These observations lead us to look for an improved analysis and design technique providing an easier development of reusable units (genericity, tailorability), and a higher level of modelling, together with a better object abstraction.

#### 2.4 Object-Oriented Methodology for HDL's Based Designs

The history of programming languages may be regarded as a progression from low level constructs towards high level of abstractions, that enable the programmer to specify programs in a more abstract manner thus allowing problem related abstractions to be captured more directly in a program. This development towards high level languages was partly motivated by the need to verify that a program adequately implemented a specification.

Object orientation is one of the most commonly used terms in recent design methodology projects, as it is closely associated with the handling of complex systems. Object-oriented methods address aspects such as encapsulation, reuse and derivation techniques to name but a few. Encapsulation is a technique used to hide the implementation of a design. The designer uses high level constructs to describe a system's behaviour without concerns about the final implementation of the construct. Reusability is achieved through message passing techniques to get information or to modify the values of an object. Consequently, the design of the function remains safe. Finally, derivation or inheritance is one of the most promising features of Objectorientation. This concept is based on the ability to design new functions from existing ones. To achieve this, a new design will inherit all the methods of its ancestors. All these attributes are highly beneficial when applied to hardware description languages (Takeuchi 1981).

Object-orientation has proven useful for numerous purposes within HDL. It can be useful for configuration management and macro modelling of analogue devices (Mammen 1994). It also provides a means of higher level description. Some of the hardware description languages that apply Object Oriented technology are Odice (Muller 1990), Loglan (Pawlak 1987), OODE (Takeuchi 1981) and SDL (Glunz 1998). These languages adopt different approaches for the semantic and object-orientation philosophies. Pascal, Algol and LISP are used as a basis for the semantics, Simula67, Modula2 and Smalltalk for the Object Oriented Implementation.

The notion of objects, originally introduced in Simula, has significantly influenced the design of many subsequent languages (e.g. Modula and Ada). The first well-known object oriented language was Smalltalk. In Smalltalk, the data hiding aspect of objects has been combined with the mechanism of inheritance, allowing the reuse of code defining the behaviour of objects.

Both information hiding and data abstraction relieve the programmer's task when using existing code; they are no longer distracted by irrelevant implementation details. On the other hand, the code developer may benefit from information hiding as well, since they will be able to optimise the implementation without interfering with the client code.

The advantages of Object-Orientation are clear when considering the gap between system design and implementation. In a number of instances, Object-Oriented analysis has been regarded as a solution to this problem of communication. According to Coad and Yourdon (Coad 1991), Object-Oriented techniques allow us to capture the system requirements in a model that directly corresponds to a conceptual model of the problem domain. Furthermore, proponents of Object-Oriented Programming (OOP) claimed (Cox 1990) that an Object-Oriented approach enables a more seamless transition between the respective phases of the software life cycle. If this turns out to be true, changing user requirements could be more easily discussed as these changes would be less disruptive for the system and they could in principle be more easily applied to the successive phases of the development. One of the basic ideas underlying Object-Oriented analysis is that the abstractions achieved in developing a conceptual model of the problem domain will remain stable over time. Consequently, rather than focusing on specific functional requirements, attention should be given to modelling the problem domain by means of high level abstractions. Due to the stability of those abstractions, the results of analysis are likely elements for reuse.

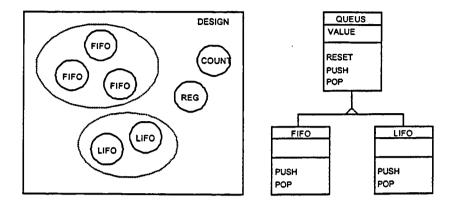

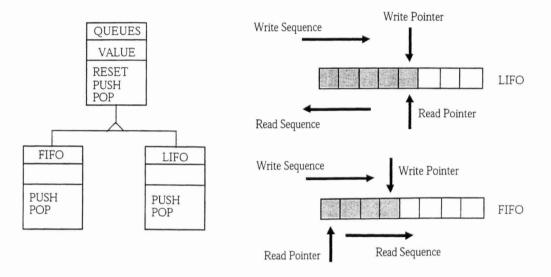

To achieve reusability, extendibility and reliability, the principles of Object-Oriented design provides the best known technical answer. Object-Orientation is a way of organising designs by focusing on a fundamental construct: the Object (Booch 1991). A design therefore represents a collection of discrete objects that incorporate both data structure and behaviours. This is often referred to as "tight binding", as opposed to the "loose binding" found in common design methodologies. The main characteristics used to support this paradigm are classification, inheritance and polymorphism. The classification enables the designer to identify groups of objects with commonalties and combine them into distinct categories. Objects are therefore seen as instances of a given class, while a class can gather an infinite number of objects exhibiting identical attributes. Figure 2-7 illustrates the Object-Oriented view of a design containing a number of FIFO (First In First Out) and LIFO (Last In First Out) objects gathered in two distinct groups. The action of grouping similar objects into classes enables further higher abstraction in the design process as illustrated by the queues class.

Figure 2-7. Object Based Design Representation.

The inheritance would also bring an extra level of organisation flexibility to hardware designs, as it refers to the action of creating a hierarchy of classes sharing common data structure and behaviours. A child class will be a refinement of a parent class, which transfers its unique properties to the inherited class. Inheritance is used to implement code sharing amongst several similar classes, therefore reducing code redundancy. In Figure 2-8 an example of inheritance is given with the queues class.

One can imagine that the two child classes FIFO and LIFO are using the same code for implementing the reset functionality. As a result, this operation would be defined at the parent class level thereby promoting code sharing. Inheritance is not just a module combination and enrichment mechanism, it also enables the definition of flexible entries that may become attached to objects of various forms whilst an HDL simulation is executing (referred as: run time), a property known as polymorphism. A polymorphic operation is characterised by its ability to adopt different behaviours depending on the object addressed.

Figure 2-8. Queues Implementation.

Considering the example given in Figure 2-8, the operation PUSH could be identical for the two child classes FIFO and LIFO and could consequently be defined at the parent class level. However, the POP operation, although having the same identifier, must behave differently. To do so, the user will "overload" the two different behaviours for the two different classes and rely on the execution program (HDL simulator) to select the appropriate one depending on the class of the selected object. As can be seen, polymorphism together with encapsulation allows a higher level of system design abstraction by postponing implementation decisions until later in the development process. Although it is difficult to find equivalents to some of these new principles in hardware, it is still sensible to search for similarities between software design and hardware design methodologies. It is even more relevant since the introduction of HDLs for hardware design. Indeed, a structure of hardware entities exchanging signals closely resembles the object model. This latest advance in the hardware design process is comparable to the introduction of structured procedural languages in software. Such an increase

in the abstraction level was motivated by an increase in design complexity and design effort. Already, the hardware community faces identical problems when considering large HDL descriptions. Design organisation, maintainability and reusability are some of the main issues that have to be studied.

In an effort to provide an object-oriented version of the VHDL language, the IEEE OOVHDL Study Group (<u>www.vhdl.org</u>) committee has produced a requirement and design objectives document. This document identifies the needs and main requirements for the building of an object-oriented extension. The requirements are related to many aspects of the language and the design methodology. However, from this document, eight main points have been identified.

- 1) To target higher levels of modelling in order to ease the changes to the design specifications and make designs less technology dependent.

- To simplify and speed-up the process of specifications. This should overcome the challenges faced during the specification of ever increasingly complex systems.

- To ease the addition of new functionality thereby reducing the needs for restructuring large parts of a design.

- 4) To improve the verification process by bridging the gap between implementation and specifications.

- 5) To further the level of reusability; This in turn should yield better design productivity along with higher design quality.

- 6) To cater for better documentation capabilities, to help the designs of growing reusable components libraries.

- To provide better consistency for the creation of Hardware/Software codesigns.

- To make the extension easy to learn and apply; Hence allowing a better acceptance of the new semantics by the designers' community.

Along with the above guidelines, the IEEE Object-Oriented study group enumerates a collection of concepts that the object-oriented extension has to include. Most of these concepts merely characterise the main features of an object-oriented language. These are:

- 1) Add better abstract data typing to VHDL.

- 2) Add inheritance/multiple inheritance.

- 3) Support for method calls or message passing.

- 4) Add polymorphism.

- 5) Add Dynamic creation/removal of objects.

- 6) Add documentation mechanism.

Having defined the requirements and design objectives for the creation of an extension to VHDL, we will now examine to what extent VHDL supports those objectives. We will also identify which of the VHDL constructs and mechanisms could be used as a base for the building of the language extension.

## 2.5 Object-Orientation in Standard VHDL

### 2.5.1 VHDL Encapsulation and Design Abstraction

Commonly, in most HDL based designs, not all features of the system need to be accessible by an end user of each component. The designer of a

component may therefore want to keep some features private or available only to specific users (e.g. because they are for internal use only and subject to changes so letting all users access them directly could endanger further evolution of the component). This is especially true of features (sub-programs or attributes) that reflect alternative implementation details of a design rather than its primary functionality. By keeping such features private, the component designer protects users against the effect of changes in the final implementation. This policy is known as information hiding. When elaborating a design, one may achieve different levels of information hiding. For immediate functionality (those introduced in the design itself), one may specify any required encapsulation restrictions by using the public or private mechanisms as found in C++. Obviously, when considering component design, a public feature will only be accessible through the ports of the given component. Consequently, any feature not listed in the port list will be seen as private. This component approach is somewhat limited and the VHDL language offers other constructs to achieve an even smoother encapsulation.

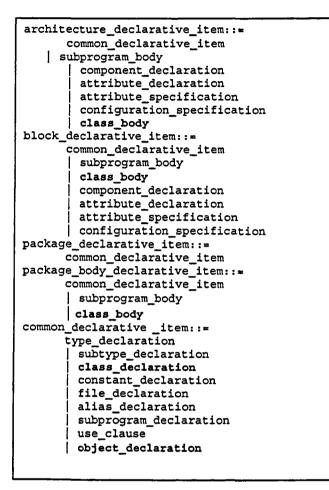

VHDL is derived from the ADA language. As such, it supports abstract data types by means of a syntactic package construct (DASC 1993). To a larger extent, this is equivalent to the class abstract data type found in most Object-Oriented programming languages. However, the benefits achieved through abstraction can be obtained only when specific coding style is used. Such a coding style involves the use of VHDL objects such as block statements, package design units and configuration design units. In many VHDL designs, a system can be characterised as a combination of several architectures, each organised as a collection of processes and related signals. A number of packages are often used throughout the design to gather common declarations. Finally, a further level of flexibility is often added to the VHDL description through the use of configuration statements. From this observation, we can now examine issues regarding the VHDL code maintainability and reusability as it stands, and derive an Object-Oriented implementation method to achieve better encapsulation and abstraction. We will use simple cases with clearly defined goals in order to discuss the various implementation possibilities.

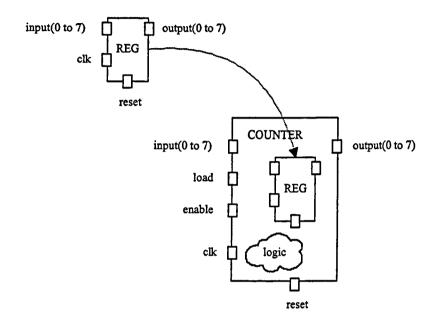

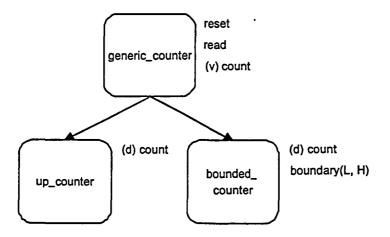

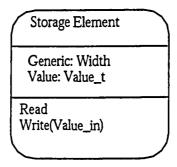

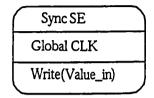

The first case implements an abstract data type for a register. An inheritance mechanism is then used to create a counter abstract data type. The description of the two abstract data types uses a generic algorithmic language. Figure 2-9 shows the implementation of the base register abstract data type. An attribute *value* is defined to hold the internal value of any instance of the register "ADT". Methods are used to implement the *reset, read,* and *write* behaviours. This model does not consider any synthesis issues and thus focuses only on behavioural aspects. Furthermore, the type of assignment is left undefined. In Figure 2-10, a counter abstract data type is designed by inheriting the capabilities of the previously defined register ADT. This new abstract data type needs only to implement the count operation to describe a complete counter. In both examples, the messages will be considered to be directly accessible by client applications – i.e. they are public.

Although these two examples do not display the full range of the Object-Orientation paradigm capabilities, they enable us to understand two of the main features: encapsulation and inheritance. To compare the two examples to standard VHDL, a simple direct analogy can be made between the abstract data type concept and the entity-architecture pair. The entity can be seen as the 'shell' of the class and performs the encapsulation; the architecture part defines the implementation of the class. Similarly, VHDL signals can be used to communicate between entities as well as to implement data attributes. Figure 2-11 demonstrates how the register class can be coded in standard VHDL with a message oriented communication scheme.

```

Body of Register

(

attribute value: bit_vector(0 to 7)

method reset

(

value becomes "00000000"

)

method read (v: out bit_vector)

(

v becomes value

)

method write (v: in bit_vector)

(

value becomes v

}

)

```

Figure 2-9. Algorithmic Description of the Register ADT.

```

Body of counter inherits register

(

method count

(

value becomes value + *00000001"

)

)

```

Figure 2-10. Algorithmic Description of the Counter ADT.

In this example, a user-defined type is created to list the different message that will be sent to the interface (entity). The message decoding is performed via the use of a "case" statement and the data attribute takes the form of the

The entity ports are defined for input values by the write method argument and output values by the read method argument. Using the same approach, the counter is implemented with standard VHDL in an Object-Oriented fashion [Figure 2-12]. Here, new functionality is added to support the 'count' operation.

```

package reg_ADT_pkg is

message_type is (reset, read, write);

type

end reg_ADT_pkg;

use work.reg_ADT_pkg.all;

entity reg is

port (message: message_type;

write_param_in: in bit_vector(0 to 7);

read_param_out: out bit_vector(0 to 7)

);

end reg;

architecture 00 of reg is

signal value: bit_vector(0 to 7);

begin

message_exec: process(message'transaction)

begin

case message is

when reset =>

value <= (others =>`0');

when read =>

read_param_out <= value;</pre>

when write =>

value <= write_param_in;</pre>

when others => null;

end case;

end process message_exec;

end OO;

```

Figure 2-1 1. Message Oriented Communication Scheme.

```

package counter ADT pkg is

type

message_type is (reset, read, write, count);

end counter_ADT_pkg;

use work.counter_ADT_pkg.all;

entity counter is

port (message: message_type;

write_param_in: in bit_vector(0 to 7);

read param out: out bit_vector(0 to 7)

);

end counter;

architecture 00 of counter is

signal value: bit_vector(0 to 7);

begin

message_exec: process(message'transaction)

begin

case message is

when reset =>

value <= (others =>`0');

when read =>

read_param_out <= value;</pre>

when write =>

value <= write_param_in;</pre>

when count =>

value <= value + "00000001";</pre>

when others => null;

end case;

end process message_exec;

end 00;

```

Figure 2-12. Register Code Re-use.

Although very similar to the register in its structure, the counter [Figure 2-12] requires a number of modifications to implement the correct functionality. The message type had to be changed as well as part of the case statement. This simple example already highlights the weaknesses of VHDL when considering code reuse.

Having looked at the most basic way of implementing an abstract data type in standard VHDL (the component object), we will now consider other options

offered by the language in an effort to demonstrate their benefits over the component object method.

A good design technique recommends the use of local variables instead of signals whenever it is possible, thus enforcing the encapsulation aspect. However, large architectures (4000 to 5000-logic gates equivalent) will contain a significant number of signals, typically implementing control functions or data path functions. These signals should be rationalised in the same way as local variables: by logically grouping related signals within the architecture. Similarly, related processes should be gathered logically to simplify any future code reuse. The VHDL language provides the "block" construct to perform this encapsulation.

Although the block construct has not generated a significant interest within the design community, we believe that if adequately used, it should prove an efficient way of increasing designers' productivity.

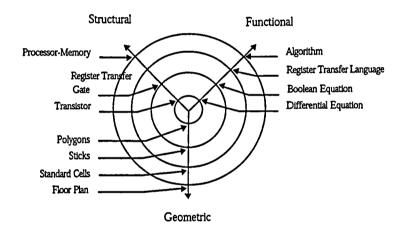

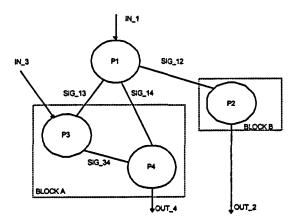

Figure 2-13. Block-Based Design Structure

In Figure 2-13, we show an architecture containing four processes that represents the design of a display driver. Process P1 is a master controller